Let's look at the main range of issues that can be attributed to the operating principle of analog-to-digital converters (ADCs) of various types. Sequential counting, bitwise balancing – what is hidden behind these words? What is the operating principle of a microcontroller ADC? We will consider these, as well as a number of other questions, within the framework of the article. We will devote the first three parts to the general theory, and from the fourth subtitle we will study the principle of their operation. You may come across the terms ADC and DAC in various literature. The way these devices work is slightly different, so don't confuse them. So, the article will consider converting signals from analogue to digital form, while the DAC works the other way around.

Definition

Before considering the operating principle of an ADC, let's find out what kind of device it is. Analog-to-digital converters are devices that convert a physical quantity into a corresponding numerical representation. The initial parameter can be almost anything - current, voltage, capacitance, resistance, shaft rotation angle, pulse frequency, and so on. But to be sure, we will only work with one transformation. This is the "voltage code". The choice of this work format is not accidental. After all, the ADC (the operating principle of this device) and its features largely depend on what measurement concept is used. This is understood as the process of comparing a certain value with a previously established standard.

ADC characteristics

The main ones are the bit depth and conversion frequency. The first is expressed in bits, and the second in counts per second. Modern analog-to-digital converters can have 24-bit resolution or conversion speeds that reach GSPS units. Please note that the ADC can only provide you with one characteristic at a time. The greater their indicators, the more difficult it is to work with the device, and the device itself costs more. But fortunately, you can get the necessary bit depth indicators by sacrificing the speed of the device.

Let's compare architectures

At the moment, there are many different ADC architectures in the world.

Each of them has its own advantages and disadvantages. There is no architecture that would achieve the maximum values of all the parameters described above. Let's analyze what maximum speed and resolution parameters the companies producing ADCs were able to achieve. We will also evaluate the advantages and disadvantages of each architecture (you can read more about the various architectures in the article on Habr). Architecture comparison table

| Architecture type | Advantages | Flaws | Maximum resolution | Maximum sampling rate |

| flash | Fast converter. The conversion is carried out in one clock cycle. | High power consumption. Limited resolution. Requires a large crystal area (comparators). It is difficult to coordinate a large number of elements (as a result, low yield). | 14 bit 128 kSa/s AD679 | 3 bit 26 GS/s HMCAD5831 |

| folding-interpolated | Fast converter. The conversion is carried out in one clock cycle. Requires fewer comparators due to preliminary “convolution” of the entire processing range into a narrower range. Occupies less space. | Errors associated with the nonlinearity of the convolution block. Delay for establishing levels in the convolution block, which reduces the maximum fs. Medium resolution. | 12 bit 6.4 GS/s ADC12DL3200 | 12 bit 6.4 GS/s ADC12DL3200 |

| SAR | High accuracy. Low power consumption. Easy to use. | Limited speed. | 32 bit 1 MSa/s LTC2500 | 10 bit 40 MSa/s XRD64L43 |

| pipeline | Fast converter. Highest accuracy among fast ADCs. Doesn't take up a large area. Has lower consumption among similar fast converters. | Pipeline delay. | 24 bit 192 kSa/s AK5386 | 12 bit 10.25 GS/s AD9213 |

| dual-slope | Average conversion accuracy. Simplicity of design. Low consumption. Resistance to changes in environmental factors. | Processes low frequency Signals (low fs). Mediocre resolution. | 12+sign bit 10 S/s TC7109 | 5+sign bits 200 kSa/s HI3-7159 |

| ∑-Δ | The highest conversion accuracy thanks to the “Noise shaping” effect (specific filtering of quantization noise) and oversampling. | Cannot work with wideband signal. | 32 bits 769 kSa/s AK5554 | 12 bit 200MS/s ADRV9009 |

I took the information for the table from the arrow website, so if I missed anything, please correct it in the comments.

Types of ADCs

The operating principle varies among different groups of devices. We will look at the following types:

- With direct conversion.

- With successive approximation.

- With parallel conversion.

- Analog-to-digital converter with charge balancing (delta-sigma).

- Integrating ADCs.

There are many other conveyor and combination types that have their own special characteristics with different architectures. But those samples that will be considered within the framework of the article are of interest due to the fact that they play an indicative role in their niche of devices of this specificity. Therefore, let's study the principle of operation of the ADC, as well as its dependence on the physical device.

Direct analog-to-digital converters

They became very popular in the 60s and 70s of the last century. They have been produced in the form of integrated circuits since the 80s. These are very simple, even primitive devices that cannot boast of significant performance. Their bit width is usually 6-8 bits, and the speed rarely exceeds 1 GSPS.

The operating principle of this type of ADC is as follows: the positive inputs of the comparators simultaneously receive an input signal. A voltage of a certain magnitude is applied to the negative terminals. And then the device determines its operating mode. This is done thanks to the reference voltage. Let's say that we have a device with 8 comparators. When ½ reference voltage is applied, only 4 of them will be turned on. The priority encoder will generate a binary code, which will be recorded in the output register. Regarding the advantages and disadvantages, we can say that this operating principle allows you to create high-speed devices. But to obtain the required bit depth you have to work hard.

The general formula for the number of comparators looks like this: 2^N. Under N you need to put the number of digits. The example discussed earlier can be used again: 2^3=8. In total, to obtain the third digit, 8 comparators are needed. This is the operating principle of the ADCs that were created first. It’s not very convenient, so other architectures subsequently appeared.

ADC bandwidth and subsampling (undersamling/sub-sampling)

Converter bandwidth

(

FPBW

-

Full Power (Analog) Bandwidth

). Typically the converter bandwidth is several Nyquist zones. This parameter should be in the specification, but if it is not, you can try to independently estimate the minimum possible bandwidth for a given ADC. During the sampling period, the UVH capacitance must be charged with an accuracy of 1 LSB. If the sampling period is , then the sampling error of the full scale signal is equal to: Solving for t, we obtain: Assuming that , we determine the minimum ADC bandwidth (for ): For example, for a 16-bit ADC with a sampling rate of 80 MSa/s and a scale of 2 V, the lower limit for the bandwidth calculated using this formula will be FPBW = 282 MHz.

Analog Bandwidth is a very important parameter when building systems that operate in subsampling mode. Let's explain this in more detail. According to the Nyquist criterion, the spectrum width of the processed signal must be at least 2 times less than the sampling frequency to avoid aliasing. What is important here is that it is the bandwidth, and not just the maximum frequency of the signal. For example, a signal whose spectrum is located entirely in the 6th Nyquist zone can theoretically be sampled without loss of information (Fig. 11). By limiting the spectrum of this signal with an anti-aliasing filter, it can be fed to a sampler with a frequency of fs. As a result, the signal will be reflected in each zone.

Rice.

11: undersampling Spectrum transfer property during sampling

Undersampling or sub-sampling occurs due to the properties of sampling. Let's consider an example, let there be a signal a(t) and its spectral density (Fig. 12). It is necessary to find the spectral density of the signal after sampling the signal.

Fig. 12: sampling of a continuous signal

Based on the filtering property of the delta function:

After sampling: where

Using the Rayleigh formula, we calculate the spectrum:

From this expression it follows that the signal spectrum will be repeated in all Nyquist zones. So, if you have a good anti-aliasing filter, then by observing the Nyquist criterion, you can digitize a signal with a sampling frequency much lower than the ADC bandwidth. But downsampling must be used carefully. It should be taken into account that the dynamic parameters of the ADC degrade (sometimes very strongly) with increasing frequency of the input signal, therefore it will not be possible to digitize a signal from the 6th zone as “purely” as from the 1st. Despite this, subsampling is actively used. For example, for processing narrowband signals, when you don’t want to spend money on an expensive broadband high-speed ADC, which in addition has high consumption. Another example is IF sampling in RF systems. There, thanks to undersampling, it is possible to exclude from the radio receiving path an extra analog link - a mixer (which transfers the signal to a lower carrier or to 0).

Successive approximation analog-to-digital converters

An algorithm is used here. In short, devices operating using this technique are simply called serial counting ADCs. The principle of operation is as follows: the device measures the value of the input signal, and then it is compared with numbers that are generated using a certain method:

- Half of the possible reference voltage is set.

- If the signal has exceeded the value limit from point No. 1, it is compared with the number that lies in the middle between the remaining value. So, in our case it will be ¾ of the reference voltage. If the reference signal does not reach this indicator, then a comparison will be made with another part of the interval according to the same principle. In this example it is ¼ reference voltage.

- Step 2 must be repeated N times, which will give us N bits of the result. This is due to carrying out N number of comparisons.

This operating principle makes it possible to obtain devices with a relatively high conversion speed, which are successive approximation ADCs. The principle of operation, as you can see, is simple, and these devices are perfect for various cases.

ADC with parallel conversion of input analog signal

In the parallel method, the input voltage is simultaneously compared to n reference voltages and determined between which two reference voltages it lies. In this case, the result is obtained quickly, but the scheme turns out to be quite complex.

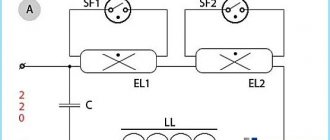

Operating principle of the ADC (Fig. 3.93)

When Uin = 0, since for all op-amps the voltage difference (U+ − U−) < 0 (U+, U− are voltages relative to the common point of the non-inverting and inverting input, respectively), the voltages at the output of all op-amps are equal to −Epit at the outputs of the encoding converter ( KP) Z0, Z1, Z2 are set to zero. If Uin > 0.5U, but less than 3/2U, only for the lower op-amp (U+ − U−) > 0 and only at its output does the voltage +Epit appear, which leads to the appearance of the following signals at the outputs of the CP: Z0 = 1, Z2 = Zl = 0. If Uin > 3/2U, but less than 5/2U, then the voltage +Epit appears at the output of the two lower op-amps, which leads to the appearance of code 010 at the outputs of the CP, etc.

Watch an interesting video about the operation of the ADC:

Parallel A/D Converters

They operate similar to serial devices. The calculation formula is (2^Н)-1. For the case considered earlier, we will need (2^3)-1 comparators. To operate, a specific array of these devices is used, each of which can compare the input and individual reference voltage. Parallel analog-to-digital converters are quite fast devices. But the design principle of these devices is such that significant power is required to maintain their functionality. Therefore, it is not advisable to use them with battery power.

Parallel ADCs

Most often, integrated comparators are used as threshold devices for parallel ADCs. The circuit diagram of a typical parallel-type ADC is shown in Figure 4.

Quite a simple scheme. The number of DA comparators is selected taking into account the code width. For example, for two digits you will need three comparators, for three - seven, for 4 - 15. The reference voltages are set using a resistive divider. The input voltage Uin is supplied to the input of the comparators and compared with a set of reference voltages taken from the divider. At the output of the comparator, where the input voltage is greater than the corresponding reference voltage, there will be a log. 1, on the rest - log. 0. Naturally, if the input voltage is equal to 0, the outputs of the comparators will be zeros. At the maximum input voltage, the outputs of the comparators will be log. 1. The encoder is designed to convert the resulting group of zeros and ones into a “normal” binary code.

Parallel ADC is the fastest of all because the comparators operate simultaneously. But there is a very significant drawback. As mentioned above, the bit capacity of such an ADC is determined by the number of comparators (and resistors, of course). At low bit depth this is not so bad. And when there are 10-12 categories. For a 10-bit ADC you will need 210 - 1 = 1023 pieces. This is no longer good. This results in the high cost of parallel ADCs. By the way, by selecting the resistances of the resistors, you can choose the transformation law - linear, logarithmic.

Analog-to-digital converter with bit balancing

It operates according to a similar scheme as the previous device. Therefore, in order to explain the functioning of a bitwise balancing ADC, the principle of operation for beginners will be discussed literally at a glance. These devices are based on the phenomenon of dichotomy. In other words, a sequential comparison of the measured value is carried out with a certain part of the maximum value. Values of ½, 1/8, 1/16 and so on can be taken. Therefore, an analog-to-digital converter can complete the entire process in N iterations (successive steps). Moreover, H is equal to the bit capacity of the ADC (look at the previously given formulas). Thus, we have a significant gain in time, if the speed of the equipment is especially important. Despite their considerable speed, these devices are also characterized by low static error.

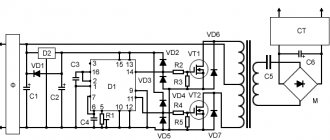

Analog-to-digital converters with charge balancing (delta-sigma)

This is the most interesting type of device, not least due to its operating principle. It consists in comparing the input voltage with what has been accumulated by the integrator. Pulses with negative or positive polarity are supplied to the input (it all depends on the result of the previous operation). Thus, we can say that such an analog-to-digital converter is a simple tracking system. But this is just an example for comparison so that you can understand what a delta-sigma ADC is. The principle of operation is systemic, but for effective functioning of this analog-to-digital converter is not enough. The end result is an endless stream of ones and zeros that flows through the digital low-pass filter. A certain bit sequence is formed from them. A distinction is made between first- and second-order ADC converters.

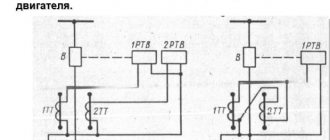

ADC with serial input signal conversion

This is a serial counting ADC, which is called a servo ADC (Fig. 3.94).

The ADC of this type uses a DAC and a reversing counter, the signal from which provides a change in the voltage at the DAC output. The circuit is configured in such a way that the voltages at the input Uin and the output of the DAC −U are approximately equal. If the input voltage Uin is greater than the voltage U at the DAC output, then the counter is switched to direct counting mode and the code at its output increases, providing an increase in the voltage at the DAC output. At the moment of equality of Uin and U, counting stops and the code corresponding to the input voltage is removed from the output of the reversible counter.

The sequential conversion method is also implemented in the time-pulse conversion ADC (ADC with a linearly varying voltage generator (GLIN)).

The operating principle of the ADC under consideration, Fig. 3.95) is based on counting the number of pulses in the time period during which the linearly varying voltage (LIN), increasing from zero, reaches the level of the input voltage Uin. The following designations are used: СС - comparison circuit, GI - pulse generator, CL - electronic key, СС - pulse counter.

Vasiliev Dmitry Petrovich

Professor of Electrical Engineering, St. Petersburg State Polytechnic University

Ask a Question

The moment in time t1 marked in the timing diagram corresponds to the beginning of measuring the input voltage, and the moment in time t2 corresponds to the equality of the input voltage and the GLIN voltage.

The measurement error is determined by the time quantization step. Key Kl connects a pulse generator to the counter from the moment the measurement begins until the moment Uin and Uclay are equal. UCh indicates the voltage at the meter input.

The code at the counter output is proportional to the input voltage. One of the disadvantages of this scheme is its low performance.

Integrating analog-to-digital converters

This is the last special case that will be considered in the article. Next, we will describe the operating principle of these devices, but at a general level. This ADC is an analog-to-digital converter with push-pull integration. You can find a similar device in a digital multimeter. And this is not surprising, because they provide high accuracy and at the same time suppress interference well.

Now let's focus on its working principle. It consists in the fact that the input signal charges the capacitor for a fixed time. As a rule, this period is a unit of the frequency of the network that powers the device (50 Hz or 60 Hz). It can also be multiple. Thus, high-frequency interference is suppressed. At the same time, the influence of unstable voltage of the network source of electricity on the accuracy of the result is neutralized.

When the charging time of the analog-to-digital converter ends, the capacitor begins to discharge at a certain fixed rate. The device's internal counter counts the number of clock pulses that are generated during this process. Thus, the longer the time period, the more significant the indicators.

Push-pull integration ADCs have high accuracy and resolution. Due to this, as well as the relatively simple construction structure, they are designed like microcircuits. The main disadvantage of this operating principle is its dependence on the network indicator. Remember that its capabilities are tied to the duration of the frequency period of the power source.

This is how a double integration ADC works. Although the operating principle of this device is quite complex, it provides quality indicators. In some cases this is simply necessary.

What is bit resolution and why is it important?

In the early days of data acquisition, 8-bit ADCs were common. As of this writing, 24-bit ADCs are the standard for most data acquisition systems designed to make dynamic measurements, and 16-bit is considered the minimum resolution for signals in general. There are a number of low-cost systems that use 12-bit ADCs.

Since each bit of resolution effectively doubles the conversion resolution, systems with 24-bit ADCs provide 2^24 = 16,777,216. Thus, the single-voltage input signal can be divided into more than 16 million Y-steps.

The 16,777,216 steps for a 24-bit ADC are significantly better than the maximum theoretical 65,656 steps for a 16-bit ADC. Thus, the higher the resolution, the better the shape and accuracy of the wave functions. The same applies to the time axis.

Compare 24-bit resolution (orange) and 16-bit resolution (gray)

DualCoreADC® Technology and Why It's Important

One of the long-standing engineering problems with the amplitude axis is dynamic range. For example: what if we have a signal that is usually less than 5 volts, but can sometimes fluctuate upward sharply? If we set the ADC resolution to 0-5V, the system will be completely overloaded if the signal exceeds this level.

One solution would be to have two channels set to different gains; and send 0–5 V data to one of them, and with a higher amplitude to the other. But this is very inefficient: we cannot use two channels for each input signal - this will reduce the performance of the data acquisition system by half. Data analysis after each measurement will also become more complicated and time-consuming.

DualCoreADC® technology solves this problem by using two separate 24-bit ADCs per channel and automatically switching between them in real time to create a single, continuous channel. These two ADCs always measure the high and low gain of the input signal. This ensures full measurement of the sensor range and prevents signal clipping.

Video explaining Dewesoft's DualCoreADC technology

With DualCoreADC® technology, SIRIUS data acquisition systems achieve 130 dB signal-to-noise ratio and over 160 dB dynamic range. This is 20 times better than typical 24-bit systems can provide.

We choose an APC with the operating principle we need

Let's say we are faced with a certain task. Which device should we choose so that it can satisfy all our needs? First, let's talk about resolution and accuracy. Very often they are confused, although in practice they very weakly depend on one another. Remember that a 12-bit A/D converter may have less accuracy than an 8-bit A/D converter. In this case, resolution is a measure of how many segments can be extracted from the input range of the signal being measured. Thus, 8-bit ADCs have 28=256 such units.

Accuracy is the total deviation of the resulting conversion result from the ideal value that should be at a given input voltage. That is, the first parameter characterizes the potential capabilities that the ADC has, and the second shows what we have in practice. Therefore, a simpler type (for example, direct analog-to-digital converters) may be suitable for us, which will satisfy the needs due to high accuracy.

To have an idea of what is needed, you first need to calculate the physical parameters and build a mathematical formula for the interaction. Static and dynamic errors are important in them, because when using different components and principles for constructing a device, they will have different effects on its characteristics. More detailed information can be found in the technical documentation offered by the manufacturer of each specific device.

Introduction

I would like to start with an interesting philosophical question: if an analog signal is infinity, do we lose an infinite amount of information when digitizing the signal? If this is true, then what is the point of such an ineffective transformation? In order to answer this question, let's understand what analog-to-digital signal conversion is. The main graph that reflects the operation of the ADC is the conversion transfer characteristic. In an ideal world, this would be a straight line, meaning that each analog signal level would have a single digital equivalent.

1: Ideal ADC performance However, due to the presence of various types of noise, we cannot increase the ADC bit capacity indefinitely. That is, there is a limit that limits the minimum price of the scale division. In other words, by decreasing the scale division, sooner or later we will “run into” noise. Yes, of course, you can make at least a 100-bit ADC, but most of the bits of this ADC will not carry useful information. That is why the ADC characteristic has a step form, which is equivalent to the presence of a finite bit capacity of the ADC. When designing a system, it is necessary to select an ADC that would ensure no loss of information during digitization. In order to choose a converter, you need to understand what parameters characterize it. ADC parameters can be divided into 2 groups:

- Static

- characterize the ADC with a constant or very slowly changing input signal. These parameters include: the maximum and minimum permissible value of the input signal, bit depth, integral and differential nonlinearity, temperature instability of conversion parameters, etc. - Dynamic

- determine the maximum conversion speed, the maximum frequency of the input signal, noise and nonlinearity.

Example

Let's take a look at the SC9711 ADC. The operating principle of this device is complex due to its size and capabilities. By the way, speaking about the latter, it should be noted that they are truly diverse. So, for example, the frequency of possible operation ranges from 10 Hz to 10 MHz. In other words, it can take 10 million samples per second! And the device itself is not something solid, but has a modular structure. But it is used, as a rule, in complex technology, where it is necessary to work with a large number of signals.