Basic functions and composition of the processor

The processor is responsible for performing the operations provided by its instruction system.

When executing a program, the central processor of the microprocessor system ensures the execution of all functions provided by the program. These include:

- generating the address of commands or data stored in RAM;

- fetching commands from memory and decrypting them;

- receiving data from RAM, performing arithmetic, logical and other operations on them, determined by the command code, and transferring the processed data to external devices or memory;

- generation of status, control and time signals necessary for the normal operation of internal nodes, as well as external devices and memory;

- temporary storage of the results of completed operations, addresses, generated status signals and other data;

- receiving request signals from external devices and servicing them.

What does the processor consist of?

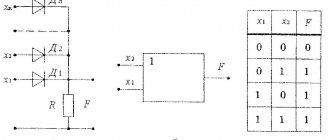

To perform the listed functions, the processor must have the necessary set of hardware. The main functional blocks of the processor are (Fig. 2.2.1):

- block of arithmetic and logical operations that processes incoming data. The list of operations performed depends on the type of microprocessor. Most processors perform the following operations: arithmetic addition and subtraction; logical operations OR, AND, NOT, exclusive OR; increment and decrement operations; logical and arithmetic shifts to the right and left. As for multiplication and division operations, in 8-bit processors they are performed in software; in 16-bit processors, special instructions are provided for their implementation. The block of arithmetic-logical operations is built on the basis of a binary adder with accelerated transfer circuits, registers for temporary storage of operands and shift registers, combinational circuits for generating logical conditions, decimal correction circuits and other functional units;

- command processing unit , designed for receiving and decoding commands, as well as for generating control signals for data processing nodes;

- address generation unit , which provides addressing to external memory and external devices. Its main nodes are the program counter, stack pointer, incrementer-decrementor, address register;

- a block of registers performing the functions of super-RAM internal memory, functions of temporary storage of operands, etc.;

- synchronization and control unit , which coordinates the work of all processor nodes;

- internal bus , which is used for communication between individual blocks and nodes of the processor. In general, it includes buses for transmitting data, addresses and control signals.

As examples, consider the structural and functional organization of 8- and 16-bit processors.

Composition of an eight-bit processor

To describe the main components of an 8-bit processor, we will use Fig. 2.2.2, which shows the block diagram of the 8080 processor (KR580VM80A).

The Arithmetic Logic Unit (ALU) allows you to perform the following operations on 8-bit operands:

- arithmetic addition of two operands with the transfer of the carry to the high digit (and without it) and subtraction with the transfer of the loan to the low digit (and without it);

- logical addition, multiplication, XOR and comparison;

- four types of cyclic shifts;

- arithmetic operations on decimal numbers.

When performing operations, one of the operands enters the ALU through accumulator A and additional register 1, the other operand through additional register 2. Cyclic shifts are performed only on the contents of accumulator A. The results of operations performed in the ALU are also placed in the accumulator.

Decimal correction block

When summing decimal numbers, correction of the result may be required, for which the microprocessor has a decimal correction unit. When adding, each digit of a decimal number (digit) is represented by a four-bit binary code (nibble, tetrad), for example, code 8421. Addition of nibbles occurs according to the rules of binary arithmetic. If the amount is more than 9, then there is a need for a correction. The correction is carried out by additionally adding the binary number 0110 (6) to the result obtained. This is due to the fact that the weight of the fifth digit of a binary number is 16 decimal units, and the weight of the highest digit of a decimal number is 10, i.e. the difference is 6.

If the result of addition is 10... 15, then adding the number 6 (0110)2 will result in the appearance of 1 in the fifth digit of the nibble. This bit “goes” to the most significant nibble and takes with it the “addition” (6), leaving the correct result. In the case when the result is 16... 18, a unit appears in the fifth digit, the value of which (before transfer) corresponds to 16 in decimal calculation. After transferring the unit of the fifth digit to the most significant nibble, its value becomes equal to 10. Thus, the transfer is accompanied by a decrease in the result by 6 decimal units, which also requires its correction. The correction principle is illustrated in two examples.

An incorrect result is detected by the presence of ones in the two most significant digits (3rd and 2nd), in the third and first, or by the presence of a carryover to the next tetrad.

Sign register

The ALU is directly connected to a 5-bit register of attributes (flags), in which the result of certain arithmetic and logical operations is recorded. The register contains five triggers:

- a carry trigger that generates a signal C = 1 if, when performing addition and shift operations, a carry unit appears from the most significant bit;

- an additional carry trigger that generates a signal V = 1 if, when performing an operation with binary decimal codes, a unit appears from the third bit (the most significant bit of the low-order nibble);

- a zero trigger that produces a signal Z = 1 if the result of the operation is zero;

- a sign trigger that generates a signal S = 1 if the value of the most significant bit of the operand (in two's complement code) is equal to one, i.e., the result of the operation is a negative number;

- a parity trigger that produces a signal P = 1 if the result of the operation contains an even number of ones.

These triggers ensure the execution of conditional jumps in the program. For example, if the result of the previous operation is zero, then the zero trigger is set to the unit state (Z = 1), and the condition for moving to another part of the program will be satisfied. The distribution of bits in the condition sign register in a byte during transmission via the data bus is as follows:

Processor registers

Registers, including the program counter and stack pointer, are accessed through multiplexers using a register selector.

General purpose registers (GPRs) play the role of accumulators when they contain processed data, or pointers when they store operand addresses. Registers B, C, D, E, H, L can be used in the program as separate 8-bit registers or as 16-bit register pairs BC, DE, HL. The name of the pair B, D, H always corresponds to the name of the first register of the pair, which stores the most significant byte of a 16-bit number. The 16-bit register H serves as an address register: with indirect register addressing, it stores the execution address coming from main memory.

The W and Z registers are not software accessible and are used to execute instructions within the microprocessor. They store the second and third bytes of the command.

Information exchange between the microprocessor and external devices is carried out through a bidirectional buffer register, and addressing to memory and external devices is carried out through a 16-bit address register. The peculiarity of the buffer and address registers is that in addition to the state of logical zero and one, they provide a third state in which the output resistance of the registers is infinitely large. In this state of the microprocessor, external devices directly access memory.

Command pointer, or program counter (Program Counter - PC).

The counter indicates the address where the next command byte is located in memory (3-byte formats are used for commands). Instruction bytes are usually selected in ascending order of their addresses. Therefore, after fetching each next byte, the increment-decrement circuit increases the contents of the program counter by one. Before fetching a command, the address of its first byte is entered into the counter. During the selection process of a 3-byte instruction, the counter is incremented three times. The normal order of addresses may be changed. To do this, the counter provides the ability to record the starting address of that part of the program, called a subroutine, that must be executed.

Stack pointer

The stack pointer (StackPointer -SP) is a 16-bit register designed to quickly address a special type of memory called the stack. Stack memory is used when servicing interrupts and is characterized by the fact that the most recently received data is selected from it first.

The return address to the interrupted program while the microprocessor is processing the subroutine, the contents of the accumulator, and the attribute register are stored on the stack.

Control block

The first byte of the command being executed is written to the command register. In the command decoder, signals are generated, under the influence of which the microprogram is launched in the control device to perform the required operation. Microprograms for operations determined by the microprocessor command set are “hardwired” into the control memory. The control device inputs receive:

- two non-overlapping sequences of clock pulses (F1, F2) with period T;

- readiness signal (READY) of external devices and memory for information exchange with the microprocessor;

- request signal from external devices to interrupt (INT) execution of the main program and transition to execution of interrupt service routines;

- a request signal from external devices to seize buses (HOLD), as a rule, to organize information exchange via a direct memory access channel;

- reset signal (RESET), which initializes the microprocessor.

From the output of the control device, signals are taken to control the internal nodes (these connections are not shown in Fig. 2.2.3) of the processor and external devices.

To control external devices, the following are developed:

- a synchronization signal (SYNC), indicating the beginning of each machine cycle - the period of time required for one processor access to external devices or memory;

- receive signal (DBIN), indicating the processor is ready to receive data;

- a wait signal (WAIT), indicating that the processor is in a waiting state;

- HLDA signal, which confirms that the buses are in a high-resistance state and external devices can access memory directly, bypassing the processor;

- interrupt enable signal (INTE), indicating that the interrupt enable trigger in the control unit is in a logical one state, in which it is possible to receive request signals;

- signal ¯Output(¯WR= 0), indicating that the processor has issued information to the data bus for writing it to memory or transmitting it to external devices.

Introduction

All technical equipment can be divided into two large categories, namely, digital equipment and analog. Each category has its own advantages and disadvantages. Equipment based on analog components has excellent performance with fairly low power consumption, but its parameters are not stable enough. Equipment made on the basis of digital technologies have increased stability of their parameters, which is their main advantage. Advances in digital technology have also made it possible to significantly reduce the energy consumption of digital equipment, which is also an excellent characteristic of them.

Are you an expert in this subject area? We invite you to become the author of the Directory Working Conditions

Composition of a sixteen-bit microprocessor

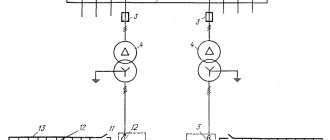

The block diagram of a 16-bit processor (8086) is shown in Fig. 2.2.3.

The microprocessor contains:

- arithmetic logic unit (ALU) with a standard set of operations;

- flag register or status word register , reflecting the state of the processor after each instruction is executed. For example, the Z flag fixes the zero result of an ALU operation;

- eight 16-bit general purpose registers (RON) designed to store addresses/data: AX (AH, AL), DX (DH, DL), CX (CH, CL), BX (VN, BL), BP, SP DI ,SI;

- address generation and bus control unit , which provides address generation by summing the contents of one of the index registers (DI, SI) with an address from memory, temporary multiplexing of the data/address bus (SD/A) , automatic filling of the command queue buffer with the following commands. The address generation and bus control block contains a buffer register, an adder and bus control logic;

- command register , designed to receive commands from external memory;

- control device , which provides processor synchronization, control of machine cycles and bus capture, servicing interrupt requests from external devices;

- command queue buffer , allowing you to store up to six bytes of a received command;

- four 16-bit segment registers (CS, SS, DS, ES) and a program counter (Instruction Pointer - IP), which take part in the formation of the address.

Purpose of control signals

Control signals are supplied via the control bus control panel (Fig. 2.2.3) of the microprocessor (MP), which operates in two modes: minimum and maximum configuration. Signals used in both modes:

- CLK - Clock pulses intended for MP synchronization

- RESET — Resetting the MP to its initial state

- READY Ready signal of the host, polled by the MP in the third cycle of each machine cycle

- NMI Non-maskable request signal

- INTR Maskable vector request signal. The mask is the interrupt enable flag

- IF A16/S3…A19/S6 A16…A19 - high-order bits of addresses when accessing memory.

- S4 S3 - segment register code (00 -ES; 01 -SS; 10 -CS, BB or interrupt; 11 -DS).

- S5 - signal for indicating the IF interrupt flag; updated at the beginning of each clock cycle.

S6 = 0 with S5 =IF = 1 BHE#/S7 OUT# = 0 is supplied to the senior H-bank when accessing memory.

S7—signal about the processor state, where # is the inversion sign RD# Reading memory and port (in minimal configuration mode)

TEST# Output of the chip interrogated by the command

WAIT#: with TEST = 1 – polling mode after 5 clock cycles; when TEST = 0 - standby mode MN/

MX# Minimum/maximum configuration mode switching

In the minimum configuration mode (MN/MX = 1), the MP generates the following control signals:

ALE Address strobe when writing it to an external buffer register

M/IO# Select memory/port exchange

DT/R# Select the exchange direction or write/read mode

WR# Write (edging) to memory or BB port

DEN# Enable data transfer via data bus

HOLD, HLDA Bus acquisition request and acquisition confirmation signals for direct memory access

Signals for maximum configuration mode (MN/MX = 0): S2# S1#

S0# MP cycle status or type code: 000—interrupt confirmation; 001 - reading BB port; 010 — recording to the BB port; 011 - stop; 100 - command sample; 101 - memory reading; 111 - passive state QS1

QS0 Queue status code: 00 - passive state (no operation); 01 — clearing the queue; 10 - fetching the first byte of the command; 11 - fetching the next byte of the command RQ/GT1,RQ/GT0

Bus acquisition request, DMA acquisition enable, and bus release signals

When designating signals, the symbol # is used, meaning inversion, i.e. A# = A.

Let's take a closer look at the organization of the command queue and the principle of forming addresses using segment registers.

Command queuing During program execution, a significant amount of time is spent fetching commands from memory. Therefore, the address generation and bus control unit tries to keep the command queue buffer filled by reading subsequent commands from memory during the execution of the current command, when the SD/A remains free.

After the current command completes, the next command is read from the buffer. Since no memory access is required, processor performance increases. When executing conditional and unconditional jump commands associated with transferring control to another memory cell, the buffer is cleared, after which it begins to fill again.

Principle of address formation

Let's set the task to form a 20-bit address (addr20), providing access to 220 = 1M bytes of memory, using two 16-bit registers. Each of the 16-bit registers provides access to 216 cells or 64K bytes of memory. Therefore, we will allocate a segment with a capacity of 64K bytes in 1M byte of memory with the condition that the least significant digit of its hexadecimal code of the starting address is equal to zero, i.e. the address code has the form XXXX0

h, where X = 0 or 1, h is the hexadecimal code designation. We will select one of the registers as a segment selector (sel), the other as an offset register (offset). Let's represent the address as the sum addr20 = 1 6 x sel +offset =XXXX0h +YYYYh.

From the expression it follows that by changing the contents of the selector (ХХХХ h) and the offset register (YYYYh) from 0000 h to FFFFh, 164x164 combinations of addresses can be obtained. However, among them there are the same codes. The total number of memory cells with different addresses is 220 – 24 + 216.

In Fig. 2.2.4, and shows how you can provide access to memory with a number of cells of 220 (or a capacity of 1 M bytes when using single-byte cells).

Processors use segment registers (CS code registers, SS stack registers, DS data registers, and an additional ES register) as selectors, which can be thought of as segment pointers, and general purpose registers (IP program counter, SP stack pointer, SP stack pointer) as offset registers. base pointer BP and auto-incremental SI and auto-decremental DI addressing registers). The following register pairs are possible:

CS<—>IP,

SS<—>SP,

DS<—>BP,

DS<—>SI,

ES<—>DI. In Fig. 2.2.4, b shows as an example the implementation of the addressing principle using a pair

SS <—>SP.

8-bit microcontrollers

8-bit microcontrollers are the simplest and cheapest products of this class, aimed at use in relatively simple mass-produced devices. Microcontrollers in this group usually execute a relatively small set of instructions (50–100), using the simplest addressing methods. The main areas of their application are industrial automation, automotive electronics, measuring equipment, television, video and audio equipment, communications, and household equipment.

8-bit microcontrollers are characterized by Harvard architecture:

- with a separate internal memory for storing programs, which is used as mask-programmable ROM (ROM), once-programmable ROM (PROM) or electrically reprogrammable ROM (EPROM, EEPROM or Flash) with a capacity from several units to tens of kilobytes;

- with a separate internal memory for storing data, which is used as a register block, organized in the form of several register banks, or RAM. Its volume ranges from several tens of bytes to several kilobytes.

If necessary, it is possible to additionally connect external memory of commands and data with a capacity of up to 64–256 KB or more.

To improve performance, many models of 8-bit microcontrollers implement the principles of RISC architecture, ensuring the execution of most instructions in one clock cycle.

About coprocessors

To expand the functionality and improve the performance of the central processor, a microprocessor system may contain additional processors, or coprocessors. For example, in the first generations of computers, the 80287 coprocessor was used to expand the functions of the 80286 central processor.

The 80287 coprocessor is designed to perform operations on floating point (comma) numbers that would require a lot of machine time from the main processor. Therefore, such a coprocessor is called a numerical processor, a processor for processing numerical data, a processor

NDP (Numeric Data Processor) or mathematical coprocessor. The coprocessor performs complex operations such as long operand division, trigonometric functions, square roots, and logarithms 10 to 100 times faster than the main processor. The accuracy of the calculation results is significantly higher than the accuracy provided by the computing modules included in the processors themselves. The gain is realized only when executing programs written to share the coprocessor with the main processor. When working together, addition, subtraction and multiplication operations are performed by the main processor and are not transferred to the coprocessor.

The coprocessor has its own command system (instructions), which differs from the processor command system. The executing program must itself determine the presence of a coprocessor and then use the instructions written for it. Most programs designed to use coprocessors detect its presence and use the capabilities provided.

Coprocessors are most effectively used in programs with complex mathematical calculations: spreadsheets, databases, statistical programs and computer-aided design systems. When working with text editors, the coprocessor is not used.

80486 and later processors use integrated coprocessors. They are implemented in the form of a floating point unit (FPU), which is part of the processor, and are located on the same chip. Floating-point instructions are part of the processor instruction system.

Historical reference

Three projects that were completed almost simultaneously lay claim to primacy in the creation of M. In 1968–70, she developed M for the F-14A fighter, which consisted of several crystals and was intended to calculate the speed, altitude and position of the wings (data declassified in 1998). On Sept. 1971 announced M. TMS1802NC for use in calculators (in 1973 the company received a patent for M. on a single chip). However, most experts in the field will calculate. technicians give primacy, which announced in November. 1971 about the creation of M. Intel 4004 (on one chip), which was also developed for calculators, but later began to be positioned as universal; simultaneously processed 4 binary bits, contained 2300 transistors, operated at a frequency of 740 kHz, occupied an area of \u200b\u200bthe chip. 24 mm2, performed 60 thousand operations per second (was hundreds of times less productive than large computers of that time). In 1972, the 8-bit M. Intel 8008 appeared, which contained 3500 transistors. M. RCA 1802 (1976) - the first radiation-resistant M., used in space. probes. In 1978, the Intel 8086 M (29 thousand transistors) was created, which was the most successful 16-bit M (it laid the foundation for the x86 family). Increasing the bit capacity of memory made it possible to increase the address space of available memory and computer performance. Version 8088 of this M was used in the widely used personal computer IBM PC. The first 32-bit M. on a single chip was created in 1980. In 1985, the commercially successful 32-bit M. Intel 386 (275 thousand transistors) appeared. The first commercial microscope with 64-bit mathematical memory addressing was released in 1991 (MIPS Technologies R4000); previously released M. (for example, Intel i860, 1989) had the ability to perform 64-bit operations on data, but were deprived of 64-bit addressing. The first 64-bit x86-compatible M was the AMD Opteron, released in 2003, implementing the AMD64 architecture.

Internal CPU resources

These include:

- types of data that the processor is capable of recognizing and processing, i.e., performing various actions and operations on them;

- software-accessible registers designed to store data and addresses during program execution;

- Addressing Modes , or addressing methods implemented by the processor. By addressing method we mean the labels for determining or calculating the so-called effective address (EA), which provides access to operands or transfer of control. Internal resources are built into the processor and reflected in its instruction system and therefore are used not only when programming applied tasks, but also during direct program execution.

The processor architecture provides the most commonly required data types, registers, and addressing modes. Each processor supports several data types, addressing modes, and contains a specific set of internal registers.

Diversity, availability and skillful use of resources help improve system performance. Missing or missing resources allow software modeling, but reduce productivity.

To develop a system program, system resources are strictly linked to the processor architecture, which include memory and I/O addresses, interrupt requests, and direct memory access channels. They provide virtual memory management, multitasking, and security controls. System resources form the basis of Protected Mode capabilities.

Features of Russian microprocessors

From 1998 to this day, it has been developing microprocessors in the domestic segment. The results are impressive - stable production of RISC systems, introduction of the Elbrus series into military-defense complexes, space stations and classified bases for data transmission with the maximum level of encryption. The merits are serious, although to many ordinary people such “successes” seem ridiculous, against the backdrop of global giants like Intel and AMD.

Yes, the achievements are not the same, but the goals are completely different, right? Elbrus can hardly be regarded as a gaming chip capable of running all modern entertainment in maximum quality - it is, first of all, a system for ultra-fast data processing (primarily for military purposes) in field and even extreme conditions.

History of the development of processors from Russia:

- 1998 . The first SPARC model with a frequency of 80 MHz.

- year 2001 . Adjusting the SPARC model, increasing power, reducing energy consumption, working on the third version of the processor with a frequency of 500 MHz.

- 2004 . Introduced E2K, a new generation processor capable of operating in almost any environment.

- 2005 year . The appearance of the first samples of Elbrus, experiments and a look into the future - many years of struggle for world leadership in the field of modern technologies lie ahead...