Триггеры различных видов зачастую входят в состав различной простой схемотехники, где не требуется применение микроконтроллеров. Они могут сохранять ранее установленные значения, изменять их, производить запись логического нуля или единицы. D-триггер является одним из наиболее распространённых видов таких устройств. Он позволяет осуществлять задержку сигналов, а также хранить информацию на протяжении нужного времени.

Какие бывают триггеры

Действие триггеров основывается на определенных принципах, зависящих от их типа. Эти логические устройства принимают входные сигналы, которые ими и управляют. Выходная информация зависит от сигнала, поступившего на вход и от полученного на предыдущем этапе. Следовательно, D-триггер реагирует и на существующие в данный момент значения, и на поступившие ранее.

Условно-графическое обозначение (УГО) Д-триггера демонстрирует, что у него вход D является информационным, а второй, обозначенный буквой С, используется для синхронизации записи и позволяет сохранить на выходе состояние, которое было на входе в момент его изменения в 1 (что называется режим «прозрачности»).

Триггер может быть синхронный (тактируемый) и асинхронный (нетактируемый). В первом случае устройство учитывает тактовые сигналы. В любой вычислительной системе все действия выполняются с привязкой к сигналам такого типа с целью обеспечения согласованной работы.

Использование тактовых сигналов в синхронных триггерах означает, что срабатывание по заложенному принципу происходит не в любой момент времени, а лишь тогда, когда на управляющем входе наблюдается определенное событие. Например, если осуществляется переход тактового импульса от максимального значения до нулевого или наоборот. У асинхронных устройств такой привязки нет. В них переход из одного режима в другой выполняется перепадом напряжения.

Триггеры представляют собой достаточно сложные электронные схемы, но они обеспечивают выполнение простого и понятного принципа преобразования входных сигналов в выходные. D-триггеры называют еще «защелками», что наглядно поясняет их принцип работы.

Что такое Д триггер

Триггерами называют устройства, способные длительное время поддерживать определенное состояние на выходе. Как правило, они контролируют соответствующие уровни напряжения. Изменения происходят при определенной комбинации входных сигналов.

Простейшие устройства этой категории создают по схеме RS. Они запоминают состояние сигнала, поданного на один из входов. Чтобы устранить процесс сбоев, который вызывают паразитные колебания при переходе сигнала из ноля в единицу и обратно, применяют синхронизацию. Этим дополнительным сигналом устанавливают точное время (интервал) для возможных изменений.

В обозначении Д триггера отмечена главная особенность. Буквой «Д» (D лат.) маркируют вход, на который подают информационный сигнал. Другой («С») используют для синхронизации записи. Отсутствие активности на нем исключает изменение базового состояния. Такое решение, в отличие от RS, позволяет изменять состояние с применением только одного источника данных.

Как работает D-триггер

Входы D-триггера разделяются на информационные (управляющие) и вспомогательные. Последние предназначены синхронизировать работу устройства. Первые устанавливают на входе определённую комбинацию двоичных чисел, которая будет учитываться при формировании выходного сигнала. Управляет логикой работы тактовый сигнал. Именно он определяет момент срабатывания триггера, а от его характеристик зависит состояние выходного сигнала.

D-триггер называют еще триггером задержки, поскольку он способен задерживать входной информационный сигнал на один такт. Время задержки определяется частотой импульсов синхронизации. Если информационный сигнал изменится, то выходной повторит его изменение, но лишь после того как тактовый сигнал примет значение, равное единице. Пока его значение будет оставаться нулевым, сигнал на выходе меняться не будет.

Работа любого D-триггера отражается в таблице истинности. Как видим, таблица истинности статического D-триггера достаточно простая. Она показывает, что нулевое значение управляющего сигнала обеспечивает хранение предыдущего значения сигнала на выходе на протяжении любого нужного периода времени. На практике речь идёт о том времени, когда к устройству подключено электропитание.

В представленной таблице истинности приведена информация о срабатывании D-триггера при значении C = 1. На практике применяется ещё один вариант, когда срабатывание происходит по переднему фронту импульса. То есть, выходное значение становится равным входному в тот момент, когда значение управляющего импульса меняется с нуля на 1. Логический элемент, в котором используется управление по уровню напряжения, называется статический D-триггер, а по фронту — динамический.

Когда применяется управление по фронту, срабатывание происходит при изменении управляющего значения. Может применяться два варианта — по переднему фронту или по заднему. При использовании первого варианта значение меняется с 0 на 1, второго — с 1 на 0.

Помимо таблицы, для описания работы логических элементов используются еще временные диаграммы.

Усложнённый вариант триггера

Иногда используется усложнённый вариант, когда добавляется ещё один вход. Обычно его обозначают буквой R. Если на него подается сигнал с нулевым значением, он не оказывает никакого влияния на работу элемента. В том случае, когда на вход R поступает сигнал с единичным значением, происходит сброс Q в 0. Этого же можно добиться на классическом D-триггере, если использовать C = 0 и D = 0.

Схемы реализации D-триггера

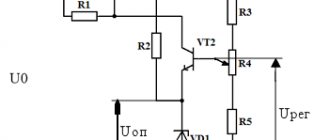

Существуют разные варианты построения данного логического элемента. Ниже представлена схема одноступенчатого D-триггера с применением элементов И-НЕ. Входы у него прямые статические. Элементы, обозначенные DD1.1 и DD1.2, задействованы в схеме управления, а на остальных построен асинхронный RS-триггер.

Роль каждого элемента будет проще понять, изучив принцип работы Д-триггера. Из схемы видно, если C = 0, то логическая операция И создаст нулевое значение независимо от вторых входных значений на DD1.1 и DD1.2. Операция отрицания сформирует единицу на выходе обоих этих элементов.

На входе третьего элемента будет два значения: единица и отрицание Q. Операция И на выходе сформирует отрицание Q. Отрицание приведёт к тому, что на выходе будет значение Q, совпадающее с тем, которое здесь было раньше.

На четвертый элемент поступят единица и Q. Результатом применения И будет Q. После применения отрицания на выходе этого элемента будет отрицание Q. Следовательно, и в этом случае значение не изменится.

Теперь нужно рассмотреть ситуацию, когда на управляющем входе единичное значение. Если D = 0, то после применения И будет получен ноль, а в результате отрицания выходным значением DD.1 станет единица, которая будет передана на вход DD1.2.

В DD1.2 на входе имеется две единицы, значит операция И сформирует 1, а отрицание даст 0. Следовательно, на DD1.4 на выходе будет единица, что соответствует нулевому значению Q. По такому же принципу рассчитываются остальные варианты.

Схему D-триггера можно получить из синхронного RS-триггера за счет введения дополнительного элемента И-НЕ1, соединяющего оба инверсных входа в один информационный. Это позволяет исключить состояние неопределенности для S и R.

Существуют еще комбинированные D-триггеры. Они имеют входы S и R, предназначенные для асинхронной установки логического 0 и 1. С помощью этих входов устройству можно придать первоначальное определенное состояние.

На схеме видно, что из 6 элементов И-НЕ построен D-триггер, его принцип работы следующий: при наличии 1 на входе R и нуля на C, D, S будут оставаться закрытыми элементы с первого по пятый. Шестой элемент при этом будет открытым, то есть, Q = 1, а /Q = 0. Первый элемент откроется, если с входа S будет снят нулевой сигнал. Состояние остальных элементов не изменится.

Когда на вход С поступит единичный сигнал, на всех входах третьего элемента появится такой же сигнал, в результате чего он откроется. Шестой элемент при этом закроется и /Q = 1. Затем на входы пятого элемента также поступят единичные сигналы, и он примет открытое состояние, а Q = 0. В результате после переключения триггера на выходе Q появится сигнал идентичный тому сигналу, который был на входе D до переключения, то есть, Qn+1 = Dn = 0. Если же с входа С снимается единичный сигнал, состояние триггера не меняется.

Достаточно просто схема D-триггера реализовывается на КМОП микросхемах. В подобных устройствах функции логических элементов И выполняют обычные транзисторные ключи.

После поступления синхросигнала высокого уровня на вход С транзистор №1 открывается, обеспечивая поступление сигнала с D на Q. При этом задействуется первый инвертор. В данной ситуации второй транзистор остается закрытым. Он отключает инвертор, построенный на транзисторах VT1 и VT3. Включается этот инвертор после поступления низкого потенциала на вход С.

D-триггеры входят в состав многих микросхем. Например, в микросхеме ТМ2 содержится два таких элемента, ТМ5, ТМ7, ТМ8 — четыре, ТМ9 — шесть.

Устройство Д триггера

Скважность импульсов

Проще всего представить функциональность на основе элементарных логических элементов. Второе название триггеров данной категории – «защелка», наглядно поясняет основные принципы работы.

Схема Д триггера

На рисунке, кроме основных, отмечены входы. Вне зависимости от сигналов синхронизации, с их помощью переводят изделие в нулевое или единичное состояние. Таким образом реализован принцип приоритетности, так как активация S и R блокирует входные вентили C.

Применение D-триггеров

Способность сохранять информацию позволяет применять D-триггеры для реализации устройств памяти. Эти работающие элементы способны сохранять нужный режим на выходе до тех пор, пока не будет подан управляющий сигнал для изменения. Триггер даёт возможность, как вносить двоичную информацию, так и хранить и считывать её.

Понимая, что такое Д-триггер, его можно применить для создания регистра-защёлки. Эти устройства важны в определённых ситуациях. Иногда сигнал длится на протяжении очень небольшого промежутка времени и микросхема может не успеть среагировать на него. В подобных случаях выгодно использовать ещё одну микросхему, на которой сохранятся необходимые значения на протяжении времени, достаточного для выполнения нужных действий.

Одно из основных назначений D-триггера — использование в счетном режиме. Чтобы заставить его работать в качестве счетчика импульсов, достаточно на вход D подать сигнал с его собственного инверторного выхода. В таком режиме по приходу каждого импульса на вход С триггер будет менять свое состояние на противоположное, как показано на временной диаграмме.

Делитель частоты — устройство, способное изменять частоту выходного сигнала относительно входного значения. Используя каскадное соединение нескольких элементов, можно построить делители частоты, обладающие различными коэффициентами деления. Два D-триггера, соединенных последовательно, обеспечивают получение выходного сигнала, частота которого в четыре раза меньше по сравнению с той, что была на входе. Три последовательно соединенных элемента будут делить ее на восемь, а четыре — на шестнадцать.

При создании цифровых схем, действие которых синхронизируется единым тактовым генератором, очень часть бывает необходимо добиться синхронизации действующей схемы и внешнего входного сигнала. То есть, асинхронный сигнал должен преобразоваться в синхронный для всей системы, в которую он поступает. Эту задачу можно решить путем установки D-триггера.

Триггер способен выполнять логическую функцию и при этом поддерживать обратную связь. Именно поэтому его используют при создании многих устройств, предназначенных для запоминания, хранения, передачи и преобразования информации. Найти эти элементы можно в самых разных приборах, включая и устройства цифровой микроэлектроники.

2.9.3. Триггер со счетным входом (т–триггер)

Основной особенностью Т-триггера является то, что при поступлении на его вход очередного импульса триггер изменяет свое состояние на противоположное. Существуют две структуры Т–триггеров: однотактная и двухтактная. Однотактные схемы в настоящее время практически не используются из-за их недостаточной надежности.

На рис. 2.36 представлена логическая схема Т-триггера со счетным входом, построенная на элементной базе “И-ИЛИ-НЕ”. Как видно из схемы, выходы триггера Q связаны со входами обратными связями.

Рис. 2.36. Логическая схема двухтактного Т- триггера

Двухтактная схема используется для того, чтобы с помощью обратной связи создать механизм запоминания предыдущего состояния триггера на время переходного процесса при установке триггера первой ступени в противоположное состояние.

УГО Т-триггера показано на рис. 2.36. Как видно из временной диаграммы (рис.2.37), при поступлении очередного импульса на счетный вход триггера его состояние меняется на противо-положное. При этом между моментами срабатывания триггеров первой и второй ступеней имеется временная задержка, равная длительности синхроимпульса. Частота импульсов, поступающих на вход триггера, делится на два, т.е. сам триггер срабатывает в 2 раза реже.

Рис. 2.37. Временная диаграмма работы Т-триггера

В табл. 2.16 представлена таблица переходов триггера со счетным входом. В ней символ “ ┐” обозначает инверсию сигнала Q.

Рис.2.38. УГО Т- триггера

Таблица 2.16

| Сt | Q1t+0,5 | Qt+1 |

| 0 | Q1t | Qt |

| 1 | ┐Qt | ┐Qt |

2.9.4. Универсальный d-триггер (триггер-задержка)

Его особенность в том, что он имеет один информационный вход (название D от Delay). Триггер запоминает (задерживает) информацию, которая поступает по одному информационному каналу. Триггер также называется универсальным, так как на его основе можно построить все другие типы триггеров. Существуют две структуры D-триггера: однотактная и двухтактная.

На рис. 2.39 показано УГО однотактного D –триггера.

Рис. 2.39 . УГО однотактного D-триггера

Рис. 2.40. Логическая схема однотактного D-триггера

На рис. 2.40 представлена логическая схема D -триггера, построенная на ЛЭ типа “ И-НЕ”. Особенность этой схемы состоит в том, что имеется только один информационный вход D.

В табл. 2.17 дана таблица переходов однотактного D-триггера.

Таблица 2.17

| D | Ct | St | Rt | Qt+1 |

| 1 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | Qt |

| 0 | 0 | 1 | 1 | Qt |

Из этой таблицы видно, что при С =1 на выходе триггера устанавливается состояние, равное значению входа D.

Рис. 2.41. Логическая схема двухтактного D-триггера

На рис. 2.41 представлена логическая схема двухтактного D -триггера, построенного на элементной базе “И-НЕ”.

УГО двухтактного D –триггера представлено на рис. 8.13. Эта схема отличается от двухтактного R-S -триггера тем, что у нее только один информационный вход D.

Рис. 2.42. УГО двухтактного D-триггера

Рис. 2.43. Т-триггер на основе двухтактного D-триггера

На основе двухтактного D-триггера можно построить Т-триггер, при этом роль счетного входа выполняет вход С (рис.2.43).

studfiles.net