Главная > Теория > RS триггер

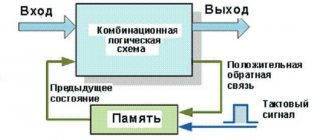

Базовый строительный блок, который делает возможной компьютерную память, а также используется во многих последовательных логических устройствах является триггерной, или бистабильной, схемой. Только два взаимосвязанных логических входа составляют основную форму этой схемы, выход которой имеет два стабильных состояния. Когда схема запускается в какое-либо из них с помощью подходящего входного импульса, она будет «запоминать» это состояние до тех пор, пока оно не будет изменено дополнительным входным импульсом, или пока не отключится питание.

Логическая микросхема

Классификация последовательных схем

Последовательные схемы могут быть использованы для простых триггеров или для создания более сложных систем: устройств памяти, счетчиков, регистров сдвига. Они подразделяются на три основные категории:

- Асинхронные, меняющие статус при включении;

- Синхронные, согласованные с тактовым сигналом;

- Комбинированные, реагирующие на запуск импульсов.

Важно! Если схема зависит от внешнего входа, то она является асинхронной. Если состояния меняются в зависимости от тактового сигнала, то она синхронная. Для сохранения состояния присутствует обратная связь, когда частично сигнал с выхода идет опять на вход.

Что такое RS триггер

Хлопковый выключатель и его особенности

RS триггер можно рассматривать как однобитную память, поскольку он сохраняет входной импульс даже после его прохождения. Триггеры разных типов могут быть изготовлены из логических вентилей. Наиболее используемыми являются И-НЕ и ИЛИ-НЕ. Самые применяемые – И-НЕ. Это связано с их универсальностью, то есть можно имитировать любую из других стандартных логических функций.

Схема триггера РС (Set-Reset) – одно из простейших последовательных соединений, состоящее из двух перекрестно включенных вентилей. Выход каждого из них подключен ко входу другого, что дает форму положительной обратной связи.

RS триггер

Триггер РС имеет два активных входа (S и R) и два выхода (Q и Q̃ (not-Q)). Для синхронных схем добавляется вход С с тактовым сигналом.

У RS триггера принцип работы можно описать так:

- Состояние установки. Пусть вход одного вентиля R находится на логическом уровне 0, а вход другого S – на уровне 1. На выходе первого элемента Q̃ получается 1 (логический принцип И-НЕ). Этот выход одновременно подается на вход первого вентиля. В результате оба его входа соответствуют 1, а на выходе Q – 0. Если вход R меняется на 1, а S остается на прежнем уровне 1, то первый вентиль получает по обратной связи еще 0 на вход, и выход Q̃ будет неизменным – 1. Триггерная цепь заперта или установлена с Q, равным 0, и Q̃, равным 1, вне зависимости от подаваемого сигнала;

- Состояние сброса. Является альтернативным неизменным состоянием. Изначальные его условия: логический уровень сигнала на входе первого вентиля R – 1, а второго S – 0. Выход Q̃ имеет значение 0, Q соответствует 1. Так как у второго вентиля один из входов имеет логику 0, то на выходе Q – 1 (по логическому принципу И-НЕ). Здесь опять работает обратная связь, и первый вентиль получает на вход 1. Две единицы на входе обеспечивают 0 на выходе Q̃. При изменении заданной логики входа S на 1 и сохранении того же сигнала 1 на входе R на выходе Q̃ остается 0, а на Q – 1. То есть фиксируется новое состояние, не зависящее от смен входного значения.

Важно! На вход S (set) должен быть подан сигнал, который переводит схему в состояние, когда Q равно единице. Сигнал на входе R (reset) производит сброс схемы в нулевое состояние.

Урок 8.4 Триггеры, регистры, счетчики

На предыдущем уроке мы рассмотрели логические элементы, состояние сигнала на выходе которых однозначно определяется состояниями сигналов на входах.

Логические элементы служат основой для создания более сложных цифровых устройств, одним из которых является триггер. Триггер – это целый класс электронных устройств, которые могут длительно находиться в одном из двух устойчивых состояний после прекращения сигнала, меняющего состояние. Состояние выхода триггера определяется не только сигналами на его входах, но и предыдущим состоянием устройства. Таким образом, триггер является простейшей однобитной ячейкой памяти.

RS-триггер

Самый простой триггер можно получить из двух логических элементов 2ИЛИ-НЕ:

Cхемотехническое обозначение:

Такая схема представляет собой асинхронный RS-триггер.

Он имеет два входа: S (set) – установка, R (reset) – сброс, и два выхода: Q (прямой) и Q с чертой сверху (инверсный, НЕ_Q).

При подаче сигнала логического нуля на оба входа триггера, его выходы будут установлены в произвольное состояние. Допустим, Q = 0, а НЕ_Q =1. Если на вход S подать «1», то состояние выхода Q скачкообразно изменится на «1», а НЕ_Q — на «0». И это состояние будет поддерживаться в независимости от того «0» или «1» подано на вход S, что и является проявлением свойства памяти.

Соответственно, при подаче уровня «1» на вход R выход Q станет «0», а НЕ_Q – «1».

Длительность устанавливающих импульсов может быть очень короткой, и ограничена физическим быстродействием логических модулей, из которых построен триггер.

Ситуация, когда на входах R и S действует высокий уровень, является недопустимой, поскольку при этом схема не может работать корректно. В этом есть недостаток RS-триггера.

RS-триггер также можно построить из двух элементов И-НЕ, такие элементы более распространены:

Установка и сброс триггера на элементах 2И-НЕ, в отличие от предыдущего, производится низким уровнем входного сигнала.

Если к последней схеме добавить еще два вентиля 2И-НЕ, то мы получим синхронный RS-триггер.

Изменение состояния такого триггера производится только при воздействии на вход С (Clock) синхронизирующего (тактового) импульса.

D-триггер

Немного изменив схему синхронного RS-триггера, можно получить D-триггер. (D-delay, задержка). У него только один информационный вход D.

Если на этот вход подать «1», а затем подать импульс на вход C, то на выходе Q будет «1», если на вход подать «0», затем импульс на C, то на выходе Q будет «0». Таким образом, D-триггер осуществляет задержку информации, поступающей на вход.

Если вход D соединить с выходом НЕ_Q, то триггер будет менять свое состояние при каждом изменении состояния входа С от «0» к «1» . При изменении от «1» к «0» состояние триггера меняться не будет. Таким образом, частота выходных импульсов будет вдвое меньше частоты входных импульсов. Такой триггер называется счетным или T-триггером. Делитель частоты используется очень широко в цифровой технике.

Существует разновидность синхронного RS-триггера, не имеющая запрещенной комбинации – JK-триггер. Он имеет три входа: J (вместо R), K (вместо S), и C. Если на оба информационных входа подана «1», то JK-триггер работает как счетный T-триггер с входом C.

Регистр хранения

На триггерах можно строить более сложные цифровые устройства, например такие, как регистры. Регистры предназначены для хранения многобитовой информации, то есть чисел, записанных в двоичном коде.

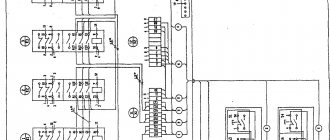

Рассмотри трех битовый регистр хранения на D-триггерах:

Каждый триггер может хранить один разряд (бит) числа. Вход R служит для установки выходов всех триггеров в нулевое (исходное) состояние перед записью числа, которое подается на входы D0,D1 и D2. При подаче импульса на вход C производится запись информации с этих входов. Информация может храниться сколь угодно долго, пока на вход С не подаются импульсы и подается питание.

Регистр сдвига

Другой разновидностью регистров является регистр сдвига. Он предназначен для преобразования информации путем ее побитного сдвига в ту или иную сторону. На следующем рисунке приведена схема простейшего регистра сдвига информации вправо (по схеме):

В отличие от регистра хранения выход предыдущего триггера соединен с входом последующего. Информация в виде логического уровня подается на вход первого (крайнего слева) триггера. При воздействии импульса на входе C присутствующая на входе D информация записывается в первый триггер. При подаче второго импульса информация из первого триггера переписывается во второй триггер, а в первый записывается информация, которая в этот момент присутствует на входе D, и так далее. Таким образом, с подачей каждого синхроимпульса информация в регистре сдвигается вправо на 1 разряд.

Сдвиговые регистры используются во многих схемотехнических решениях при построении цифровых устройств, прежде всего для преобразования последовательного кода в параллельный, а также для выполнения арифметических операций (умножения и деления на 2)с двоичными числами, организации линий задержки, формирования импульсов заданной длительности, генерирования псевдослучайных последовательностей (кодов) и т.п.

Счетчик

Еще один класс цифровых устройств, которые можно построить на триггерах – счетчики. Как следует из названия, они осуществляют счет входных импульсов в заданном коде и могут хранить результат.

Простейший счетчик с последовательным переносом можно получить с помощью счетных T-триггеров:

Подачей импульса на вход R счетчик приводится в исходное состояние, когда на выходах Q1-Q3 – уровень логического нуля.

На вход C подаются импульсы для счета. С приходом заднего фронта первого импульса первый (левый) по схеме триггер устанавливается в «1». Если читать код справа налево, то он соответствует единице. Для нашего трехразрядного счетчика это код 001. С приходом второго импульса в «1» переключается второй триггер, а первый переключается в «0». Таким образом, код на выходах счетчика будет 010, что соответствует десятичной цифре 2. Следующий импульс установит код 011, то есть 3. Трехразрядный счетчик может досчитать до кода 111, что соответствует десятичной цифре 7. При этом наступает так называемое переполнение счетчика, и с приходом следующего импульса счетчик обнулится.

Поскольку триггеры счетчика соединены последовательно, то и переключаться они будут также последовательно. Этот процесс отображен на графике, из которого видно, что время задержки переключения tз будет удваиваться и утраиваться. С увеличением числа разрядов задержка может оказаться неприемлемой, что является недостатком счетчиков с последовательным переносом.

Для повышения быстродействия применяются счетчики с параллельным переносом, что достигается одновременной подачей входных импульсов на входы всех триггеров счетчика. Это реализуется с помощью введения в схему логических элементов И:

Из схемы видно, что на вход второго триггера счетный импульс поступит только тогда, когда на выходе первого триггера будет «1», а на третий – когда «1» будет на выходах и первого, и второго триггеров. Очевидно, что с увеличением числа разрядов необходимо увеличивать как число логических элементов И, так и число их входов, что, в свою очередь, является недостатком такого типа счетчиков.

Регистры и счетчики, в свою очередь, могут применяться для построения более сложных цифровых устройств: сумматоров, ОЗУ и ПЗУ (оперативных и постоянных запоминающих устройств), АЛУ (арифметическо-логических устройств), входящих в состав процессоров, и так далее, к все более сложным цифровым устройствам.

В следующей серии статей мы начнем знакомство с микроконтроллерами — замечательным классом цифровых микросхем, которые являются настоящими компьютерами, умещающимися в одной микросхеме, и входящими входят в состав большинства электронных устройств, от кофемашины до космического корабля!

Таблица истинности

Работу триггера РС можно представить в таблице истинности:

- Q устанавливается на логическое значение 1, если применяется 0 на входе S;

- Изменение S-входа на единицу на выходную логику не влияет. 0-импульс был запомнен Q;

- Q сбрасывается на 0 с помощью логического 0, подаваемого на вход R;

- Когда R возвращается к 1, на Q запоминается 0.

Таблица истинности

Для условий 2-й и 3-ей строки таблицы Q̃ является величиной, обратной Q. Однако в первой строке оба входа равны 0, что делает Q̃ = Q = 1, и они не будут являться противоположными логическими состояниями. На практике такое состояние не допускается, так как триггер РС теряет стабильность.

В последней строке на обоих входах присутствует логическая единица, выходы Q̃ и Q будут находиться в противоположных состояниях, но не ясно, какими конкретно значениями будут обладать. Они будут соответствовать запоминаемым с последнего входного импульса.

Помимо применения логики И-НЕ, можно построить простые триггеры, используя два перекрестно соединенных вентиля И-ИЛИ. Схема работает аналогично. Только запрещенное состояние будет при наличии обоих входных сигналов, равных единице.

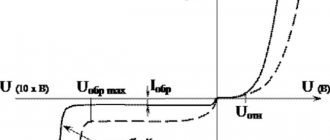

Временные диаграммы

Скважность импульсов

Таблицы истинности иногда не являются лучшим методом описания последовательной схемы. Часто предпочтительнее временная диаграмма синхронизации, которая показывает, как логические состояния в разных точках цепи меняются со временем.

Временная диаграмма RS триггера

На рисунке видно, что в первый момент времени t1 оба сигнала высокие, что вызывает неопределенное состояние. Затем от t1 до t2 S равно 0, R равно 1 на выходе Q устанавливается 1. Еще два неопределенных состояния: от t2 до t3 и от t4 до t5. На промежутке t3-t4 происходит сброс схемы в 0 на выходе Q. А в пределах t6-t7 – недопустимое состояние схемы, когда R и S равны 0.

Электростанции

Временные диаграммы, также называемые импульсными диаграммами, являются вспомогательным средством для лучшего понимания работы триггера и всей схемы в целом. Входные сигналы временных диаграмм заданы заранее или могут выбираться любыми. Выходные сигналы зависят от входных сигналов. Поясним сказанное на простом примере. На рис. 7.88 изображен не тактируемый ^S’-триггер, так называемый ЛУ-триггер хранения с таблицей истинности и временными диаграммами. Таблица истинности действительна для момента времени t.

Рис. 7.88. RS-триггер хранения с таблицей истинности для момента времени tm и временной диаграммой

В момент времени tx триггер устанавливается, так как на S действует 1-сигнал. В момент времени t2 триггер сбрасывается. На выходе R сигнал 1. В момент времени /3 триггер снова устанавливается. Особенно интересен момент /4. С этого момента времени на обоих входах действует сигнал 1. Эта комбинация запрещена. Оба выхода переключаются в 1. Если в момент времени t5 на /?-вход подать 0, то Q2 также установится в 0. В точке t6 5-сигнал равен 0. Триггер остается установленным. Сброс возможен только при R = 1. В точке t7 триггер мог бы быть снова установлен. Однако он еще не установлен. Поэтому выходные состояния не изменяются. В точке ?8 Л-сигнал становится равным 1. Однако на достается 1. Снова возникает некорректная комбинация Qt = 1 и Q2 = 1. Особенно критическим является момент t9, в котором S и R сигналы одновременно снижаются до 0. Становится неясно, в какое состояние установится триггер. Комбинация S = R — 1 является запрещенной и ее следует избегать. Рассмотрим рис. 7.89. Даны входные сигналы S и R и сигнал синхронизации Т. В момент времени tx S = 1, однако к Т еще подведен 0-сигнал. Триггер не может установиться. Только к моменту времени t2 триггер установится. В точке /3 он сбросится. В точке t S становится равным 1, а в точке t R = 1.

Рис. 7.89. Тактируемый RS-триггер с доминирующим R-входом, таблицей истинности и временной диаграммой

Так как тактирующий сигнал не включен, то эти сигналы не оказывают влияния на триггер. Только в точке t6 они действуют на триггер. Теперь триггер должен был бы сброситься. Однако он уже сброшен и, следовательно, состояние выходов не изменяется. В точке t7 триггер устанавливается. В точке t% происходит сброс, так как несмотря на единичные состояния S и R входов, 7?-вход имеет приоритет. Состояние выхода Q2 находится всегда в противофазе к состоянию выхода Qv Какая временная диаграмма, соответствует Ql и Qv если бы RS-трттор с доминирующим jR-входом управлялся по переднему фронту синхроимпульса? Соответствующая временная диаграмма представлена на рис. 7.90. Триггер можно переключать только в моменты времени tv tv ty В точке tx триггер будет установлен, так как S = 1. В точке t2 триггер сбрасывается, так как S = R = 1. В точке t3 триггер снова устанавливается (S = 1). Для Qx и Q2 получается совершенно другая диаграмма, чем на рис. 7.89.

Для управляемого по одному фронту /ЙГ-триггера на рис. 7.91 получается следующая временная диаграмма. Триггер может переключаться только в моменты времени tv t2, t3, t4, ts и t6. Только в эти моменты времени подаются задние фронты С-сигнала. В точке tx триггер установится, так как /= 1. В точке tx триггер сбросится, так как К — 1. В момент времени t3 триггер должен был бы сброситься, однако так как он уже сброшен, то состояния выходов Qx и Q2 не изменяются. В точке t4 /= 1 и К= 1. Триггер переключается. Так как перед моментом времени Qx был равен 0, то после t4 Qx = 1. В точках ts и t6 триггер переключается в противоположное состояние. Состояние выхода Q2 всегда находится в противофазе к состоянию выхода Qx. В качестве следующего примера рассмотрим временные диаграммы управляемого по двум фронтам /А’-триггера (рис. 7.92). В точке tx входной сигнал / = 1 поступает в ведущий триггер. И только в момент времени t2 (с обратным фронтом синхроимпульса) на выходах появляются сигналы, соответствующие режиму установки Qx — 1 и Q2 = 0. В момент времени Г3 / = 0 и К = 0. Это режим хранения. Поэтому в точке /4 состояния выходов не меняются. В точке t5 входной сигнал К= 1 поступает в ведущий триггер. Но лишь в момент времени t6 на выходах появляются сигналы, соответствующие режиму сброса Qx = 0 и Q2= 1. В момент времени t7 J = 1 и К = 1. При такой комбинации входных сигналов триггер переключит выходы в состояния, противоположные текущим, но только в момент времени tr В точке t9 AT становится равным 1. Сброс выходных сигналов происходит в точке tl0.

Рис. 7.92. Управляемый по двум фронтам JK-триггер (MS-триггер) с таблицей истинности и временной диаграммой

Похожие статьи

JK триггер

Выпрямитель тока

Другие широко распространенные виды логических схем – JK, D и Т, которые являются разработками RS триггера на логических элементах.

Недостатки схемы И-НЕ РС триггера:

- Необходимость избегать условия, когда оба входных сигнала равны 0;

- При изменениях состояния R и S, имеющих единичный входной сигнал, правильное блокирующее действие не всегда происходит.

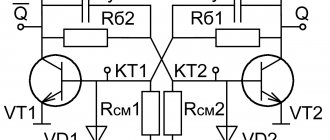

Для преодоления этих недостатков была разработана схема JK триггера. Его входы являются теми же R и S, но им присвоены буквы J и K по имени изобретателя схемы, чтобы отличить от других триггеров. JK схема отличается от RS триггера тем, что она не имеет неопределенных или запрещенных входных статусов.

JK триггер

В JK добавлена входная схема синхронизации, предотвращающая неопределенное условие вывода, которое может случиться, если R и S равны единице. Поэтому в наличии четыре возможных комбинации ввода: 1, 0, «без изменений» и «переключение». Вход J соответствует S, а K – R. Кроме того, для каждого вентиля имеется третий вход. На выходе остаются Q̃ и Q.

Перекрестная связь RS триггера позволяет использовать ранее неопределенные условия работы триггера, когда оба входных сигнала равны 1, для создания «переключателя», так как два входа могут быть блокированы.

Схема JK – это триггер SR с обратной связью, который позволяет только одному из его терминалов (SET или RESET) быть активным в любой момент времени, тем самым устраняя недопустимое условие:

- Если активен терминал SET, вход J блокируется статусом 0 (Q̃) через нижний логический элемент И-НЕ;

- Если в действии терминал RESET, вход К заблокирован статусом 0 через верхний вентиль И-НЕ.

Так как Q̃ и Q всегда разные, они могут использоваться для манипулирования входом. Для JK триггера таблица истинности принимает следующий вид.

Таблица истинности JK триггера

Когда оба входа J и K имеют единицу на входе при высоком тактовом импульсе, схема может переключаться из состояния SET в RESET и наоборот.

Триггеры

Триггеры и регистры являются простейшими представителями цифровых микросхем, имеющих внутреннюю память. Если выходные сигналы логических элементов и комбинационных микросхем однозначно определяются их текущими входными сигналами, то выходные сигналы микросхем с внутренней памятью зависят также еще и от того, какие входные сигналы и в какой последовательности поступали на них в прошлом, то есть они помнят предысторию поведения схемы. Именно поэтому их применение позволяет строить гораздо более сложные и интеллектуальные цифровые устройства, чем в случае простейших микросхем без памяти. Микросхемы с внутренней памятью называются еще последовательными или последовательностными, в отличие от комбинационных микросхем.

Триггеры и регистры сохраняют свою память только до тех пор, пока на них подается напряжение питания. Иначе говоря, их память относится к типу оперативной

(в отличие от

постоянной памяти

и

перепрограммируемой постоянной памяти

, которым отключение питания не мешает сохранять информацию). После выключения питания и его последующего включения триггеры и регистры переходят в случайное состояние, то есть их выходные сигналы могут устанавливаться как в уровень логической единицы, так и в уровень логического нуля. Это необходимо учитывать при проектировании схем.

Большим преимуществом триггеров и регистров перед другими типами микросхем с памятью является их максимально высокое быстродействие (то есть минимальные времена задержек срабатывания и максимально высокая допустимая рабочая частота). Именно поэтому триггеры и регистры иногда называют также сверхоперативной памятью

. Однако недостаток триггеров и регистров в том, что объем их внутренней памяти очень мал, они могут хранить только отдельные сигналы, биты (триггеры) или отдельные коды, байты, слова (регистры).

Триггер можно рассматривать как одноразрядную, а регистр — как многоразрядную ячейку памяти, которая состоит из нескольких триггеров, соединенных параллельно (обычный, параллельный регистр) или последовательно (сдвиговый регистр или, что то же самое, регистр сдвига).

Триггеры

Принцип работы и разновидности триггеров

В основе любого триггера (англ. — «тrigger» или «flip-flop») лежит схема из двух логических элементов, которые охвачены положительными обратными связями (то есть сигналы с выходов подаются на входы). В результате подобного включения схема может находиться в одном из двух устойчивых состояний, причем находиться сколь угодно долго, пока на нее подано напряжение питания.

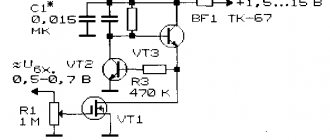

Рис. 7.1.

Схема триггерной ячейки

Пример такой схемы (так называемой триггерной ячейки) на двух двухвходовых элементах И-НЕ представлен на рис. 7.1. У схемы есть два инверсных входа: –R — сброс (от английского Reset), и –S — установка (от английского Set), а также два выхода: прямой выход Q и инверсный выход –Q.

Для правильной работы схемы отрицательные импульсы должны поступать на ее входы не одновременно. Приход импульса на вход -R переводит выход -Q в состояние единицы, а так как сигнал -S при этом единичный, выход Q становится нулевым. Этот же сигнал Q поступает по цепи обратной связи на вход нижнего элемента. Поэтому даже после окончания импульса на входе -R состояние схемы не изменяется (на Q остается нуль, на -Q остается единица). Точно так же при приходе импульса на вход -S выход Q в единицу, а выход -Q — в нуль. Оба эти устойчивых состояния триггерной ячейки могут сохраняться сколь угодно долго, пока не придет очередной входной импульс, — иными словами, схема обладает памятью.

Если оба входных импульса придут строго одновременно, то в момент действия этих импульсов на обоих выходах будут единичные сигналы, а после окончания входных импульсов выходы случайным образом попадут в одно из двух устойчивых состояний. Точно так же случайным образом будет выбрано одно из двух устойчивых состояний триггерной ячейки при включении питания. Временная диаграмма работы триггерной ячейки показана на рисунке.

Таблица 7.1. Таблица истинности триггерной ячейки

| Входы | Выходы | ||

| -R | -S | Q | -Q |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | Без изменения | |

| 0 | 0 | Не определено | |

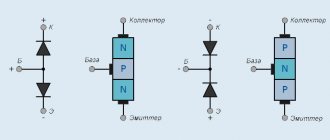

В стандартные серии цифровых микросхем входит несколько типов микросхем триггеров, различающихся методами управления, а также входными и выходными сигналами. На схемах триггеры обозначаются буквой Т. В отечественных сериях микросхем триггеры имеют наименование ТВ, ТМ и ТР в зависимости от типа триггера. Наиболее распространены три типа ( рис. 7.2):

- RS-триггер (обозначается ТР) — самый простой триггер, но редко используемый (а).

- JK-триггер (обозначается ТВ) имеет самое сложное управление, также используется довольно редко (б).

- D-триггер (обозначается ТМ) — наиболее распространенный тип триггера (в).

Примером RS-триггера является микросхема ТР2, в одном корпусе которой находятся четыре RS-триггера. Два триггера имеют по одному входу –R и –S, а два других триггера — по одному входу –R и по два входа –S1 и –S2, объединенных по функции И. Все триггеры имеют только по одному прямому выходу. RS-триггер практически ничем не отличается по своим функциям от триггерной ячейки, рассмотренной ранее (см. рис. 7.1). Отрицательный импульс на входе –R перебрасывает выход в нуль, а отрицательный импульс на входе –S (или на любом из входов –S1 и –S2) перебрасывает выход в единицу. Одновременные сигналы на входах –R и –S переводят выход в единицу, а после окончания импульсов триггер попадает случайным образом в одно из своих устойчивых состояний. Таблица истинности триггера ТР2 с двумя входами установки –S1 и –S2 представлена в табл. 7.2.

Рис. 7.2.

Триггеры трех основных типов

Таблица 7.2. Таблица истинности RS-триггера ТР2

| Входы | Выходы | ||

| -R | -S | Q | -Q |

| 1 | 1 | 1 | Без изменения |

| X | 0 | 1 | 1 |

| 0 | X | 1 | 1 |

| 1 | 1 | 0 | 0 |

| X | 0 | 0 | Не определен |

| 0 | X | 0 | Не определен |

JK-триггер значительно сложнее по своей структуре, чем RS-триггер. Он относится к так называемым тактируемым триггерам, то есть он срабатывает по фронту тактового сигнала. Примером может служить показанная на рис. 7.2 микросхема ТВ9, имеющая в одном корпусе два JK-триггера со входами сброса и установки -R и -S. Входы -R и -S работают точно так же, как и в RS-триггере, то есть отрицательный импульс на входе -R устанавливает прямой выход в нуль, а инверсный — в единицу, а отрицательный импульс на входе -S устанавливает прямой выход в единицу, а инверсный — в нуль.

Однако состояние триггера может быть изменено не только этими сигналами, но и сигналами на двух информационных входах J и K и синхросигналом С. Переключение триггера в этом случае происходит по отрицательному фронту сигнала С (по переходу из единицы в нуль) в зависимости от состояний сигналов J и K. При единице на входе J и нуле на входе К по фронту сигнала С прямой выход устанавливается в единицу (обратный — в нуль). При нуле на входе J и единице на входе К по фронту сигнала С прямой выход устанавливается в нуль (обратный — в единицу). При единичных уровнях на обоих входах J и K по фронту сигнала С триггер меняет состояние своих выходов на противоположные (это называется счетным режимом).

Таблица 7.3. Таблица истинности JK-триггера ТВ9

| Входы | Выходы | |||||

| -S | -R | C | J | K | Q | -Q |

| 0 | 1 | Х | Х | Х | 1 | 0 |

| 1 | 0 | Х | Х | Х | 0 | 1 |

| 0 | 0 | Х | Х | Х | Не определено | |

| 1 | 1 | 1 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 0 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 0 | 0 | 0 | Не изменяется | |

| 1 | 1 | 1 0 | 1 | 1 | Меняется на проти-воположное | |

| 1 | 1 | 1 | Х | Х | Не изменяется | |

| 1 | 1 | 0 | Х | Х | Не изменяется | |

| 1 | 1 | 0 1 | Х | Х | Не изменяется | |

Рис. 7.3.

Временная диаграмма работы JK-триггера ТВ9

Таблица истинности триггера ТВ9 представлена в табл. 7.3, а временная диаграмма работы — на рис. 7.3.

Cинхронные схемы

Бывает, требуется применять схемы с логическими элементами, работающими на основе изменения состояния при создании специальных условий, не зависящих от статуса входов. При этом в схему добавляется логический компонент И, имеющий 2 входа и соединенный с триггерными входами. Теперь входы R и S будут выполняться через терминал И, имеется также третий вход для тактовых импульсов. Изменение работы триггера заключается в том, что на Q̃ и Q состояние будет варьироваться из-за прохождения высокого тактового сигнала на входе, называемого «включить».

Синхронная схема RS триггера

- Когда тактовый сигнал равен 0, выходные значения элементов И идентичны, фиксируя выходные сигналы в последнем запомнившимся статусе;

- При тактовом импульсе, соответствующем единице, вся схема приобретает прозрачность и начинает работать как нормальный РС триггер. При этом оба входа воспринимают сигналы R и S.

Основным преимуществом тактового сигнала является то, что выход этого триггера можно синхронизировать со многими другими схемами и устройствами, которые используют одни и те же тактовые импульсы. Эта компоновка используется для базового расположения памяти, например, применяя различные логические состояния к диапазону из восьми триггеров, а затем посредством синхронного тактового импульса заставляя систему хранить байт данных.

Триггеры. Основные теоретические положения. Классификация триггеров. Разработка триггеров

Лекция 4 Триггеры

Основные теоретические положения

Триггер (защелка) – импульсное устройство с двумя устойчивыми состояниями. Переход из одного состояния в другое происходит в результате воздействия сигналов управления.

Выходной сигнал триггера зависит не только от входных сигналов, но и от его внутреннего состояния, то есть от значений входных переменных, которые действовали в предыдущие моменты времени. Следовательно, триггеры являются элементами памяти.

Электронные приборы с такими свойствами называются последовательными логическими устройствами.

Кроме устойчивых состояний, которые могут сохраняться неограниченно долго, имеются неустойчивые, они существуют короткое время, соизмеримое с длительностью процессов переключения в схеме.

Пример

. Простейшим триггером является выключатель освещения. Он имеет два устойчивых состояния и переключается кратковременным внешним воздействием.

Пример.

Использование кнопок без фиксации состояния для операций включения – выключения электрооборудования позволяет управлять объектами из различных мест.

При этом нет необходимости, для выключения какой либо установки, выявлять и отключать включенные кнопки. Достаточно выработать соответствующий сигнал управления силовым выключателем установки, который работает в режиме триггера (самоблокировка).

Простейшие триггеры на основе реле и инверторов представлены на рисунке 1.

Рис. 1 Триггеры на основе:

а – инверторов; б – реле; в – реле и кнопок управления

Устройство (рис. 1, а) может находиться в двух устойчивых состояниях входов – выходов, соответственно 1–0–0–1 и 0–1–1–0. Такая ячейка памяти называется бистабильной. Она может быть реализована на основе реле K

1,

K

2 с нормально замкнутыми контактами

K

1,

K

2 по схеме рис. 1, б. При подаче напряжения

U

п одно из реле сработает быстрее и разомкнет цепи питания другого реле. Однако таким устройством нельзя управлять.

Для управления триггером используются дополнительные элементы, позволяющие перевести его в то или иное положение, например, кнопки SB

1 и

SB

2 (рис. 1, в). Ими можно вручную перевести триггер из одного состояния в другое.

Указанные логические элементы, выполненные на основе реле, используются, в схемах релейной защиты, автоматики, для коммутации и развязки по напряжению в силовых исполнительных элементах.

1 Классификация триггеров

Обычно триггер имеет два выхода: Q

– прямой выход,

Q

’ – инверсный, если

Q

=1, то

Q

’=0 и наоборот. На схемах триггеры обозначаются символом

D

и порядковым номером на схеме (рис. 2). Входы обозначаются в соответствии с видом и назначением триггера (на рисунке не указаны).

Рис. 2 Обозначение триггера

Триггеры можно классифицировать по способам записи информации и управления, принципам построения, функциональным возможностям.

По способу записи информации различают асинхронные и синхронные триггеры.

Асинхронный триггер изменяет свое состояние в момент прихода сигнала на его информационные входы.

Синхронные триггеры меняют свое состояние под действием входных сигналов, только в момент прихода тактового сигнала на синхронизирующий вход С

.

Они могут использоваться в сложных цифровых устройствах, где разделение работы на временные такты, когда выполняются определенные операции, исключает путаницу и сбои.

По способу записи информации входы триггеров разделяются на статические и динамические.

Первые реагируют на состояния входов (обозначение на рис. 2) и переключаются при наличии соответствующего потенциала (уровня напряжения). Динамические входы реагируют на изменения состояния на входах и управляются переходом между потенциалами. Передним фронтом импульса из 0 в 1 (варианты обозначения на рис. 3, а) или задним фронтом из 1 в 0 (рис. 3, б).

Рис. 3 Обозначения динамических входов, а:

переключение по переднему фронту,

б: переключение по заднему фронту

По функциональным возможностям различают триггеры: RS

-триггер,

D

-триггер,

T

-триггер,

JK

-триггер,

VD

и

VT

-триггеры, а также

NV-

триггеры, которые после выключения напряжения питания сохраняют записанную в них информацию (энергетическая независимость).

2 Асинхронный

RS

-триггер

Асинхронный RS-триггер может быть реализован с помощью элементов 2ИЛИ-НЕ (рис. 4, а), таблица истинности (табл. 1). Он имеет два входа: S

(

et

) установка (

Q=1) и R

(

eset

) сброс (

Q=0).

Согласно временной диаграмме (рис. 4, б) и табл. 1, выход триггера переходит в состояние Qn+1 =1, если поступают сигналы S

=1,

R

=0 (интервал времени

t1 – t2) независимо от предшествующего состояния Qn.

При S

=0,

R

= 1 выход триггера переходит в состояние

Qn+1 = 0 (интервал t3 – t4). Когда S

=0,

R

=0 триггер сохраняет прежнее значение

Qn(интервалы t2 – t3; t4 – t5).

Комбинация сигналов S

=1,

R

=1 запрещена, т.к. на прямом

Q

и инверсном

Q’

выходе устанавливаются одинаковые значения, которые при переходе в режим хранения не удерживаются (интервал

t6 – t7).

Рис. 4 Асинхронный RS

-триггер на элементах 2ИЛИ-НЕ:

а – принципиальная схема; б – временные диаграммы работы

Таблица истинности RS

-триггера Таблица 1

| № | R | S | Q n+1 | Q’ n+1 | Название режима работы |

| 1 | 0 | 0 | Q n | Q’ n | Хранение информации |

| 2 | 0 | 1 | 1 | 0 | Установка в 1 |

| 3 | 1 | 0 | 0 | 1 | Установка в 0 |

| 4 | 1 | 1 | – | – | Запрещенное состояние |

Для получения аналитического выражения при разработке схемы асинхронного RS

-триггера

необходимо составить полную таблицу истинности (табл. 2).

Полная таблица истинности RS

-триггера Таблица 2

| № | R | S | Q n | Q n+1 |

| 1 | 0 | 0 | 0 | 0 |

| 2 | 0 | 0 | 1 | 1 |

| 3 | 0 | 1 | 0 | 1 |

| 4 | 0 | 1 | 1 | 1 |

| 5 | 1 | 0 | 0 | 0 |

| 6 | 1 | 0 | 1 | 0 |

| 7 | 1 | 1 | 0 | – |

| 8 | 1 | 1 | 1 | – |

Наборам, где Q

n

+1= 1, соответствует характеристическое уравнение:

В наборах 7, 8, где значение выхода не определено, можно указать 0 или 1 исходя из соображений простоты реализации схемы (рис. 4, а), которая составлена согласно полученному аналитическому выражению.

Асинхронный RS-триггер может быть собран на элементах 2И-НЕ (рис. 5, а), таблица истинности (табл. 3). В отличие от предыдущей схемы, триггер имеет инверсные входы.

Рис. 5 Асинхронный RS

-триггер на элементах 2И-НЕ: