Для выполнения логических операций и решать логические задачи с помощью средств электроники были изобретены логические элементы. Их создают с помощью диодов, транзисторов и комбинированных элементов (диодно-транзисторные). Такая логика получила название диодной логики (ДЛ), транзисторной (ТЛ) и диодно–транзисторной (ДТЛ). Используют как полевые, так и биполярные транзисторы. В последнем случае предпочтение отдается устройствам типа n-p-n, так как они обладают большим быстродействием.

Логический элемент «ИЛИ»

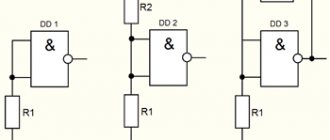

Схема логического элемента «ИЛИ» представлена на рисунке 1 а. На каждый из входов может подаваться сигнал в виде какого-то напряжения (единица) или его отсутствия (ноль). На резисторе R появиться напряжение даже при его появлении на каком – либо из диодов.

Рис. 1

Элементы или могут иметь несколько логических входов. Если используются не все входы, то те входы которые не используются следует соединять с землей (заземлять), чтобы избежать появления посторонних сигналов.

На рисунке 1б показано обозначение на электрической схеме элемента, а на 1в таблица истинности.

Булевы функции

С помощью этого калькулятора по булевой функции строится таблица истинности, определяются свойства функции и другие параметры (см. вкладку Параметры решения). При этом вводится только само логическое выражение без префикса. Например, при f(x,y,z) = x → y!z, ввести необходимо только x → y!z. Введеное выражение также можно упростить, используя законы логики высказываний (на следующем шаге выбрать параметр Упростить выражение).

(…) — ввод скобок, x -отрицание (NOT, !, ¬), & — логическое И, AND, ∧, *, v — логическое ИЛИ, OR, ∨, = — эквивалентность, ˜, ≡, ↔, ⊕ — сумма по модулю 2, | — штрих Шеффера, И-НЕ, AND-NOT, ↓ — стрелка Пирса, ИЛИ-НЕ, OR-NOT, ← — обратная импликация.

Для вложенного отрицания необходимо использовать знак !. Например, x v y = !(x v y) или x v y = x v !y

По найденной таблице истинности можно определить логические значения высказываний, например, при x=0, y=0, z=1 Чтобы проверить высказывание на истинность или ложность, функцию необходимо вводить без знака равно (=). Например, A+B→A&B=1, необходимо ввести A+B→A&B. Если в результате преобразований получится, что f=1, то высказывание истинно, если f=0 — ложно.

Логические (функциональные) элементы {v,&, ¬} являются наиболее распространенными: в силу полноты системы любую

булеву функцию (БФ) можно представить в виде суперпозиции дизъюнкции, конъюнкции и отрицания. В качестве функциональных элементов (ФЭ) можно рассматривать любые булевы функции, при этом их можно соединять друг с другом, подавая выходы одних элементов на входы других (суперпозиция БФ).

Область определения БФ E – конечное множество, поэтому БФ можно задать с помощью таблицы истинности, содержащей |E|=2n строк. Столбец значений БФ при этом представляет собой двоичное слово длиной 2n. Поэтому количество различных БФ n переменных равно 22n.

Отрицание, ¬

x f 0 1 1 0

Конъюнкция, &

x y f 0 0 0 0 1 0 1 0 0 1 1 1

Дизъюнкция, v

x y f 0 0 0 0 1 1 1 0 1 1 1 1

Сумма по модулю 2, x⊕y

x y f 0 0 0 0 1 1 1 0 1 1 1 0

Стрелка Пирса, x↓y

x y f 0 0 1 0 1 0 1 0 0 1 1 0

Эквивалентность, x↔y

x y f 0 0 1 0 1 0 1 0 0 1 1 1

Импликация, x→y

x y f 0 0 1 0 1 1 1 0 0 1 1 1

Штрих Шеффера, x|y

x y f 0 0 1 0 1 1 1 0 1 1 1 0

Другие БФ строятся из элементарных с помощью суперпозиций функций.

Основные равносильности логики высказываний

| Название | Формула |

| Закон исключенного третьего | X v !X ≡ И |

| Закон противоречия | X & !X ≡ Л |

| Закон коммутативности | X & Y ≡ Y & X X v Y ≡ Y v X |

| Закон ассоциативности | (X & Y)&Z ≡ X&(Y&Z) (X v Y) v Z ≡ X v (Y v Z) |

| Закон дистрибутивности | X&(Y v Z) ≡ X&Y v X&Z X v Y&Z ≡ (X v Y)&(X v Z) |

| Закон двойного отрицания | !!X ≡ X |

| Закон идемпотентности | X&X ≡ X, X v X ≡ X |

| Законы де Моргана | !(X v Y) ≡ !X & !Y !(X & Y) ≡ !X v !Y |

| Закон поглощения | X v X&Y ≡ X X&(X v Y) ≡ X |

| Законы склеивания | (X & Y)v(X & !Y) ≡ X (X v Y)&(X v !Y) ≡ X |

| Замена импликации | X → Y ≡ !X v Y |

| Замена эквиваленции | X = Y ≡ X&Y v !X&!Y |

Пример. Упростите выражение: (x˅y˅z)→(x˅y)*(x˅z) Упростим функцию, используя основные законы логики высказываний. Замена импликации: A → B = !A v B Для нашей функции: (x v y v z)→((x v y) (x v z)) = x v y v z v (x v y) (x v z) Упростим функцию, используя законы де Моргана: !(A v B) = !A & !B Для нашей функции: x v y v z = x y z По закону дистрибутивности: (x v y) (x v z) = x v x z v y x v y z получаем: f = x y z v x v x z v y x v y z После элементарных преобразований получаем: f = x y z v x v x z v y x v y z = x y z v x v y z f = y z v y z v x

Логический элемент «И»

Схема элемента приведена на рис. 2. Если хотя – бы к одному из входов будет сигнал равный нулю, то через диод будет протекать ток. Падение напряжения на диоде стремится к нулю, соответственно на выходе тоже будет ноль. На выходе сможет появится сигнал только при условии, что все диоды будут закрыты, то есть на всех входах будет сигнал. Рассчитаем уровень сигнала на выходе устройства:

Рис.2

на рис. 2 б – обозначение на схеме, в – таблица истинности.

Логический элемент «НЕ»

В логическом элементе «НЕ» используют транзистор (рис.3 а). при наличии положительного напряжения на входе х=1 транзистор открывается и напряжение его коллектора стремится к нулю. Если х=0 то положительного сигнала на базе нет, транзистор закрыт, ток не проходит через коллектор и на резисторе R нет падения напряжения, соответственно на коллекторе появится сигнал Е. условное обозначение и таблица истинности приведены на рис. 3 б,в.

Рис.3

Минимизация булевых функций

В данном сервисе для минимизации булевых функций используются метод Квайна и карт Карно-Вейча. После получения минимальной формы имеется возможность заново построить логическую схему. Если исходная схема понадобится в дальнейшем, то ее можно предварительно сохранить (меню Действия/Сохранить).

Сократить БФ можно, применяя некоторые равносильности логики высказываний:

- Kx v K ≡ K — тождество поглощения;

- Kx v Kx ≡ K — тождество склеивания;

- Kx v Ky ≡ K(xvy) — дистрибутивный закон,

где K- элементарная конъюнкция. Большинство методов минимизации БФ основываются на первых двух тождествах. А третье – дистрибутивный закон – уменьшает количество букв в формуле, но выводит формулу из класса ДНФ. При минимизации БФ используют различные термины (и обозначения) для полных элементарных конъюнкций (ПЭК). Наиболее часто используются термины «минтерм» и «конституента единицы». (Для полных элементарных дизъюнкций (ПЭД) используются термины «макстерм» и «конституента нуля»). Слово «конституента» означает «составляющая», а название «минтерм» исходит из определения конъюнкции, как минимального значения ее операндов. При этом используются обозначения mi — для минтерма и Mi — для макстерма. Номер i соответствует двоичной записи той оценки переменных, для которой mi=1.

Метод карт Карно

Склеить можно как целиком всю карту, либо только выделенные единицы (меню Операции).

- Склеить выделенное

- Склеить всю карту

- Удалить склейки

- Сохранить как docx

- Сохранить как png

- ✍ Помощь в решении задач

Количество переменныхСетка

После минимизации можно получить логическую схему функции и построить таблицу истинности (кнопка Далее)

Этот метод используется для БФ не более, чем с шестью аргументами и основан на тождестве склеивания: Kx v Kx ≡ K — две элементарные конъюнкции (ЭК) склеиваются, если они отличаются только знаком инверсии одного аргумента. Чтобы облегчить нахождение таких пар (четверок, восьмерок,…) склеивающихся ЭК, используют специальное представление БФ в виде таблицы – карты Карно (другое название — диаграмма Вейча). Чтобы заполнить карту Карно необходимо щелкнуть левой кнопкой мышки на соответствующую ячейку. Карта Карно обладает той особенностью, что две ПЭК, соответствующие соседним клеткам карты, отличаются знаком инверсии только одного аргумента, т.е. их можно склеивать. Причем соседними являются не только клетки, например, с номерами 1 и 3, но и клетки с номерами 12 и 8, 12 и 4, т.е. карту можно «сворачивать» в цилиндр, соединяя горизонтальные (вертикальные) ее границы. Две единицы «склеиваются» каждый раз, когда они стоят рядом в строке или столбце (карту можно свернуть в цилиндр). В результате склеивания число букв, входящих в ПЭК, уменьшается на единицу.

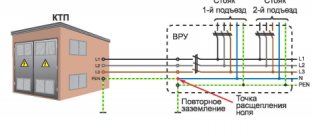

Логический элемент «ИЛИ-НЕ»

При создании различных схем на логических элементах часто применяют элементы комбинированные. В таких элементах совмещены несколько функций. Принципиальная схема показана на рис. 4 а.

Рис.4

Здесь диоды Д1 и Д2 выполняют роль элемента «ИЛИ», а транзистор играет роль инвертора. Обозначение элемента на схеме и его таблица истинности рис. 4б и в соответственно.

Минимизая функции через равносильные преобразования

см. таблицу равносильных преобразований

Алгоритм минимизии логической функции

- Замена импликации и эквиваленции.

- Упрощение функции через законы де Моргана.

- Раскрытие скобок, используя законы поглощения, исключенного третьего, противоречия.

- Минимизация через закон дистрибутивности.

Алгоритм Куайна построения сокращенной ДНФ

- Получить СДНФ функции.

- Провести все операции неполного склеивания.

- Провести все операции поглощения.

Логический элемент «И-НЕ»

Показана схема на рис. 5 а. Здесь диод Д3 выполняет роль так сказать фильтра во избежание искажения сигнала. Если на вход х1 или х2 не подан сигнал (х1=0 или х2=0), то через диод Д1 или Д2 будет протекать ток. Падение на нем не равно нулю и может оказаться достаточным для открытия транзистора. Последствием чего может стать ложное срабатывание и на выходе вместо единицы мы получим ноль. А если в цепь включить Д3, то на нем упадет значительная часть напряжения открытого на входе диода, и на базу транзистора практически ничего не приходит. Поэтому он будет закрыт, а на выходе будет единица, что и требуется при наличии нуля на каком либо из входов. На рис. 5б и в показаны таблица истинности и схемное обозначение данного устройства.

Рис.5

Логические элементы получили широчайшее применение в электронике и микропроцессорной технике. Многие системы управления строятся с использованием именно этих устройств.

(т. е. позволяют разместить большее число логических элементов в одном интегральном модуле) и не требуют использования стабилизированных источников питания.

Транзисторно-транзисторные логические элементы (ТТЛ)

ТТЛ-элементы применяются в интегральных схемах и обеспечивают высокую скорость переключения. На рис. 34.1 показана упрощенная схема логического элемента И-НЕ с многоэмиттерным транзистором T1 на входе. Когда на обоих входах присутствует логический 0, транзистор T1 насыщен и напряжение на его коллекторе близко к 0 В. Следовательно, транзистор T2 находится в состоянии отсечки, и на выходе мыимеем логическую 1. Когда на оба входа подается логическая 1, транзистор T1 закрывается и переключает транзистор T2 в состояние насыщения. В этом случае на выходе элемента мы имеем логический 0.

Рис. 34.1. Логический элемент И-НЕ (ТТЛ-типа).

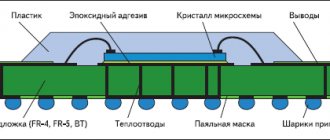

Логические элементы на полевых транзисторах

Логические схемы в настоящее время изготавливаются только в виде интегральных схем. Огромное количество логических элементов можно разместить на мельчайшем кристалле (чипе) кремния размером 1х2 мм. В силу своей простоты полевые транзисторы применяются чаще, чем биполярные транзисторы. Наиболее широко распространены логические элементы на основе так называемых КМОП-ячеек (здесь они не рассматриваются). На рис. 34.2 приведена схема логического элемента ИЛИ-НЕ на МОП-транзисторах, который работает на основе отрицательной логики. В этой схеме T1 и T2 — полевые МОП-транзисторы с каналом p

-типа (работающие в режиме обогащения). Когда на обоих входах присутствует Уровень логического 0, транзисторы T1 и T2 находятся в состоянии отсечки и на выходе мы имеем логическую 1 (-

V

DD= -20 В). Когда на один или на оба входа подается логическая 1 (например, -20 В), открываются один или оба транзистора и на выходе мы получаем логический 0.

Рис. 34.2. Логический элемент Рис. 34.3. Логический элемент на И-НЕ

ИЛИ-НЕ на МОП-транзисторах. МОП-транзисторах.

На рис. 34.3 показана схема логического элемента И-НЕ на основе полевых МОП-транзисторов с каналом п

-типа. Поскольку используется источник питания положительной полярности, данный логический элемент работает на основе положительной логики. Транзистор T3 постоянно смещен в активную рабочую область напряжением

V

DD, подаваемым на затвор, и выполняет функцию активной нагрузки логического элемента. Когда на одном или на обоих входах присутствует логический 0, один или оба транзистора находятся в состоянии отсечки, выдавая логическую 1 на выходе. Ток через транзисторы будет протекать только в том случае, когда на оба входа будет подана логическая 1, и только в этом случае мы получим на выходе логический 0.

Булевы выражения

Функции, реализуемые отдельным логическим элементом или комбинацией логических элементов, могут быть выражены логическими формулами, называемыми булевыми выражениями. В булевой алгебре используются следующие обозначения логических функций (см. табл. 34.1):

• Функция И обозначается символом точки (·). Двухвходовый (входы А и В) логический элемент И вырабатывает на выходе сигнал, представляемый булевым выражением А · В.

• Функция ИЛИ обозначается символом (+). Двухвходовый логический элемент ИЛИ вырабатывает на выходе сигнал, представляемый булевым выражением А + В.

Таблица 34.1. Булевы выражения

| Функция | Обозначение в булевой алгебре |

| И | А·В |

| или | А+В |

| НЕ | |

| И-НЕ | |

| ИЛИ-НЕ | |

| Исключающее ИЛИ | |

| Исключающее ИЛИ-НЕ |

• Логическая функция НЕ обозначается символом черты над обозначением входного сигнала. Логическая схема НЕ с одним входом А вырабатывает на выходе сигнал, представляемый булевым выражением (читается «НЕ А»).

Через эти простые функции можно выразить более сложные:

•

Функция Н-НЕ записывается как

.

•

Функция ИЛИ-НЕ записывается как

.

• Функция Исключающее ИЛИ записывается как .

Ееможно также записать, используя специальное обозначение,

.

• Функция Исключающее ИЛИ-НЕ записывается как .

Ее можно также записать, используя специальное обозначение,

.

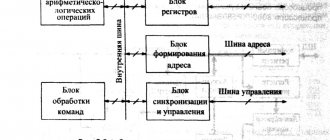

Комбинаторная логика

Рассмотрим логическую схему на рис. 34.4. Логическую функцию, выполняемую этой схемой, можно описать с помощью следующих булевых выражений.

Выходной сигнал логического элемента ИЛИ (i): A + В

Выходной сигнал логического элемента И-ИЕ (ii):

Выходной сигнал логического элемента ИЛИ (iii): (А + В) +